# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Josep Domingo-Ferrer Joachim Posegga Daniel Schreckling (Eds.)

# Smart Card Research and Advanced Applications

7th IFIP WG 8.8/11.2 International Conference, CARDIS 2006 Tarragona, Spain, April 19-21, 2006 Proceedings

Volume Editors

Josep Domingo-Ferrer Universitat Rovira i Virgili, Departament d'Enginyeria Informatica i Matematiques, Av. Paisos Catalans 26, 43007 Tarragona, Catalonia, Spain E-mail: josep.domingo@urv.net

Joachim Posegga Daniel Schreckling Universität Hamburg Arbeitsbereich Sicherheit in Verteilten Systemen (SVS) Fachbereich Informatik Vogt-Kölln-Str. 30, 22527 Hamburg, Germany E-mail: {posegga,schreckling}@informatik.uni-hamburg.de

#### Library of Congress Control Number: 2006922624

CR Subject Classification (1998): E.3, K.6.5, C.3, D.4.6, K.4.1, E.4, C.2

LNCS Sublibrary: SL 4 – Security and Cryptology

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-33311-8 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-33311-1 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

@ 2006 IFIP International Federation for Information Processing, Hofstr. 3, A-2361 Laxenburg, Austria Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11733447 06/3142 5 4 3 2 1 0

# Preface

Smart cards are an established security research area with a very unique property: it integrates numerous subfields of IT Security, which often appear scattered and only loosely connected. Smart card research unites them by providing a common goal: advancing the state of the art of designing and deploying small tokens to increase the security in Information Technology.

CARDIS has a tradition of more than one decade, and has established itself as the premier conference for research results in smart card technology. As smart card research is unique, so is CARDIS; the conference successfully attracts academic and industrial researchers without compromising in either way. CARDIS accommodates applied research results as well as theoretical contributions that might or might not become practically relevant. The key to making such a mixture attractive to both academia and industry is simple: quality of contributions and relevance to the overall subject.

This year's CARDIS made it easy to continue this tradition: we received 76 papers, nearly all of them relevant to the focus of CARDIS and presenting high-quality research results. The Program Committee worked hard on selecting the best 25 papers to be presented at the conference.

We are very grateful to the members of the Program Committee and the additional referees for generously spending their time on the difficult task of assessing the value of submitted papers. Daniel Schreckling provided invaluable assistance in handling submissions, managing review reports and editing the proceedings. The assistance of Jordi Castellà in handling practical aspects of the conference preparation is also greatly appreciated.

Financial support by the following organizations is gratefully acknowledged: IEEE Spain Section, Rovira i Virgili University (ETSE, DEIM) and Spain's Ministry of Science and Education.

Finally, we would also like to thank all those who have submitted papers to IFIP CARDIS 2006, and encourage them to stay with CARDIS in subsequent years. The authors of the accepted papers certainly deserve the highest respect, since it is they who wrote this book.

January 2006

Josep Domingo-Ferrer Joachim Posegga

# Organization

CARDIS 2006 was organized by the Universitat Rovira i Virgili, Catalonia, Spain.

# **Conference Organization**

| Conference General Chair | Josep Domingo-Ferrer              |

|--------------------------|-----------------------------------|

|                          | (Universitat Rovira i Virgili,    |

|                          | Catalonia, Spain)                 |

| Program Committee Chair  | Joachim Posegga                   |

|                          | (University of Hamburg, Germany)  |

| Advisory Committee       | José A. Delgado-Penín             |

|                          | (IEEE Spain Section Chair, Spain) |

#### **Program Committee**

**Boris Balacheff** (Hewlett-Packard Labs, UK) Bertrand du Castel (Axalto, USA) Josep Domingo-Ferrer (Universitat Rovira i Virgili, Catalonia, Spain) Dieter Gollmann (TU Hamburg-Harburg, Germany) Louis Guillou (France Télécom, France) Pieter Hartel (University of Twente, Netherlands) Peter Honeyman (University of Michigan, USA) Dirk Husemann (IBM Research, Switzerland) Eduardo de Jong (Sun Microsystems, USA) Jean-Louis Lanet (Gemplus Labs, France)

Javier Lopez (University of Malaga, Spain) Bernd Meyer (Siemens AG, Germany) Mike Montgomery (Axalto, USA) **Pierre** Paradinas (CNAM, France) Jean-Jacques Quisquater (Université Catholique de Louvain, Belgium) Francesc Sebé (Universitat Rovira i Virgili, Catalonia, Spain) François-Xavier Standaert (Université Catholique de Louvain, Belgium) Jean-Jacques Vandewalle (Gemplus Labs, France)

# **Additional Referees**

| A. Ali<br>V. Benjumea<br>D. Bolzoni<br>E. Brier | J.B. Fischer<br>C. Fontaine<br>P. Girard<br>B. Gonzalvo | A. Martínez-Ballesté<br>A. Muñoz E. Peeters<br>H.C. Pöhls<br>E. Prouff |

|-------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------|

| R. Brinkman                                     | D. Gross-Amblard                                        | R. Roman                                                               |

| I. Buhan                                        | H. Handschuh                                            | A. Saptawijaya                                                         |

| M. Casassa-Mont                                 | K. Harrisson                                            | D. Schreckling                                                         |

| J. Castellà-Roca                                | Z. HuanGuo                                              | J. Seedorf                                                             |

| J. Cederquist                                   | M. Johns                                                | D. Simplot-Ryl                                                         |

| L. Chen                                         | M. Joye                                                 | A. Solanas                                                             |

| M. Ciet                                         | A. Kargl                                                | A. Viejo-Galicia                                                       |

| R. Corin                                        | K. Lu                                                   | L.Y. Wei                                                               |

| M. Czenko                                       | F. Macé                                                 | A. Zych                                                                |

| M. Dekker                                       | A. Maña                                                 |                                                                        |

| G.M. de Dormale                                 | W. Mao                                                  |                                                                        |

# Table of Contents

# **Smart Card Applications**

| Design, Installation and Execution of a Security Agent for Mobile<br>Stations                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| William G. Sirett, John A. MacDonald, Keith Mayes,<br>Konstantinos Markantonakis                                                                            | 1   |

| Towards a Secure and Practical Multifunctional Smart Card<br>Idir Bakdi                                                                                     | 16  |

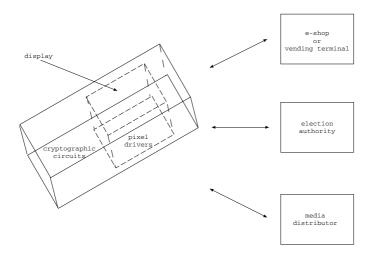

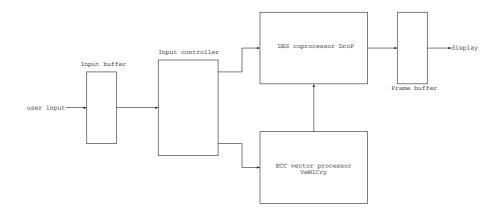

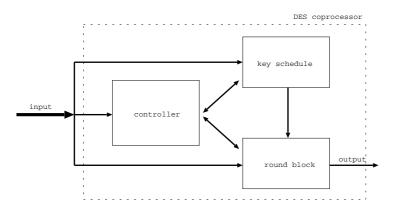

| Implementing Cryptography on TFT Technology for Secure Display<br>Applications<br>Petros Oikonomakos, Jacques Fournier, Simon Moore                         | 32  |

| Terros Orkonomakos, Jacques Fournier, Simon Moore                                                                                                           | 32  |

| A Smart Card-Based Mental Poker System<br>Jordi Castellà-Roca, Josep Domingo-Ferrer, Francesc Sebé                                                          | 48  |

| A Smart Card Solution for Access Control and Trust Management for<br>Nomadic Users<br>Daniel Díaz Sánchez, Andrés Marín Lopez,<br>Florina Almenárez Mendoza | 62  |

| Smart Cards and Residential Gateways: Improving OSGi Services with<br>Java Cards                                                                            |     |

| Juan Jesús Sánchez Sánchez, Daniel Díaz Sánchez,<br>José Alberto Vigo Segura, Natividad Martínez Madrid,<br>Ralf Seepold                                    | 78  |

| Zero Footprint Secure Internet Authentication Using Network Smart<br>Card                                                                                   |     |

| Asad M. Ali                                                                                                                                                 | 91  |

| An Optimistic NBAC-Based Fair Exchange Method for Arbitrary Items<br>Masayuki Terada, Kensaku Mori, Sadayuki Hongo                                          | 105 |

# Side Channel Attacks

| Generic Cryptanalysis of Combined Countermeasures with Randomized |     |

|-------------------------------------------------------------------|-----|

| BSD Representations                                               |     |

| Tae Hyun Kim, Dong-Guk Han, Katsuyuki Okeya, Jongin Lim           | 119 |

| Amplifying Side-Channel Attacks with Techniques from Block Cipher     |     |

|-----------------------------------------------------------------------|-----|

| Cryptanalysis                                                         |     |

| Raphael CW. Phan, Sung-Ming Yen                                       | 135 |

|                                                                       |     |

| Power Analysis to ECC Using Differential Power Between Multiplication |     |

| and Squaring                                                          |     |

| Toru Akishita, Tsuyoshi Takagi                                        | 151 |

|                                                                       |     |

# Smart Card Networking

| 165 |

|-----|

|     |

|     |

| 179 |

|     |

|     |

| 192 |

|     |

# **Cryptographic Protocols**

| Anonymous Authentication with Optional Shared Anonymity                                                           |     |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Revocation and Linkability                                                                                        |     |

| Martin Schaffer, Peter Schartner                                                                                  | 206 |

| SEA: A Scalable Encryption Algorithm for Small Embedded                                                           |     |

| Applications                                                                                                      |     |

| François-Xavier Standaert, Gilles Piret, Neil Gershenfeld,<br>Jean-Jacques Quisquater                             | 222 |

| Low-Cost Cryptography for Privacy in RFID Systems<br>Benoît Calmels, Sébastien Canard, Marc Girault, Hervé Sibert | 237 |

| Optimal Use of Montgomery Multiplication on Smart Cards<br>Arnaud Boscher, Robert Naciri                          | 252 |

| Off-Line Group Signatures with Smart Cards<br>Jean-Bernard Fischer, Emmanuel Prouff                               | 263 |

# **RFID Security**

| Analysis of Power Constraints for Cryptographic Algorithms in |     |

|---------------------------------------------------------------|-----|

| Mid-Cost RFID Tags                                            |     |

| Tobias Lohmann, Matthias Schneider, Christoph Ruland          | 278 |

| Noisy Tags: A Pretty Good Key Exchange Protocol for RFID Tags<br>Claude Castelluccia, Gildas Avoine | 289 |

|-----------------------------------------------------------------------------------------------------|-----|

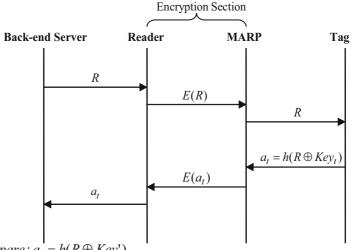

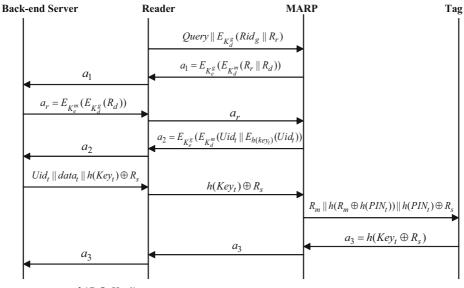

| MARP: Mobile Agent for RFID Privacy Protection<br>Soo-Cheol Kim, Sang-Soo Yeo, Sung Kwon Kim        |     |

| Formal Methods                                                                                      |     |

| Certifying Native Java Card API by Formal Refinement<br>Quang-Huy Nguyen, Boutheina Chetali         | 313 |

| A Low-Footprint Java-to-Native Compilation Scheme Using Formal Methods                              |     |

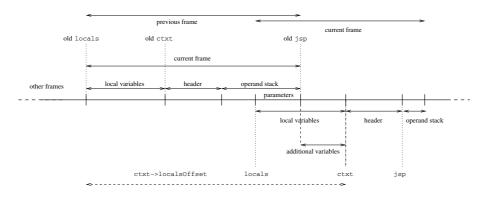

| Alexandre Courbot, Mariela Pavlova, Gilles Grimaud,<br>Jean-Jacques Vandewalle                                  | 329 |

|-----------------------------------------------------------------------------------------------------------------|-----|

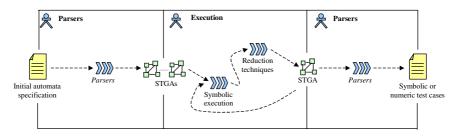

| Automatic Test Generation on a (U)SIM Smart Card<br>Céline Bigot, Alain Faivre, Christophe Gaston, Julien Simon | 345 |

| Author Index                                                                                                    | 359 |

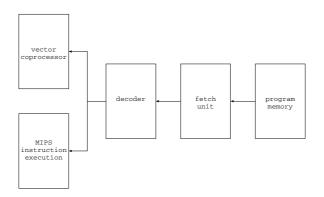

# Design, Installation and Execution of a Security Agent for Mobile Stations

William G. Sirett<sup>\*</sup>, John A. MacDonald<sup>\*\*</sup>, Keith Mayes, and Konstantinos Markantonakis

Smart Card Centre, Information Security Group, Royal Holloway, University of London, Egham, TW20 0EX, England {w.g.sirett, k.markantonakis, keith.mayes}@rhul.ac.uk, john@madgo.com

**Abstract.** In this paper we present a methodology and protocol for establishing a security context between a Mobile Operator's application server and a GSM/UMTS SIM card. The methodology assumes that the already issued Mobile Station is capable but unprepared. The proposed scheme creates a secure entity within the Mobile Station "Over The Air" (OTA). This secure entity can then be used for subsequent SIM authentications enabling m-Commerce, DRM or web service applications. To validate our proposal we have developed a proof of concept model to install and execute the security context using readily available J2ME, Java Card, J2SE and J2EE platforms, with the KToolBar MIDP2.0 emulator tool from Sun, and a Gemplus Java Card.

**Keywords:** Mobile Station, Security Agent, Application Deployment, Smart Card, GSM, Security Protocol, JSR177, MIDP2.0.

# 1 Introduction

The GSM network offers a wide scope of applications and benefits for mobile operators. The merits of a Mobile Station capable of implementing a Security Agent are well documented in the literature [17, 18]. In this paper we consider the deployment of a Security Agent that is comprised of two components: a device application executing resource-intensive tasks, and a secure entity application responsible for secure functionality. The secure entity is a tamper resistant [5] entity and in the case of this work is a GSM/UMTS SIM card. For some time the GSM network has allowed for "Over The Air" (OTA) SIM application installation with limited bandwidth capacity. To install these applications utilising a high bandwidth channel and a non-GSM specified protocol currently demands trust/keys being provided to the Mobile Device. This work considers the Mobile Device to be hostile. This raises a need for the same high bandwidth OTA functionality to be available whilst protecting against malicious equipment.

<sup>\*</sup> This work was supported by sponsorship funding from the Smart Card Centre founded by Vodafone and G&D.

<sup>\*\*</sup> This work was supported by sponsorship funding from Telefonica Móviles, España.

<sup>©</sup> IFIP International Federation for Information Processing 2006

This work establishes a security context between a Mobile Operator Application and Mobile Station and proposes an authenticated key establishment protocol. By establishing session keys independent of the network security keys, we can provide integrity, authentication and confidentially at the application layer. In the GSM/3GPP mobile architecture [24], the user security context resides in two locations, the network HLR and the Operator issued tamper resistant SIM card. The Mobile Operator generally has much less control over the Mobile device than the SIM. Consequently they are more reluctant to load sensitive components or data into the device. This motivates the division of the *Security Agent* between the device and the SIM, where the SIM is responsible for particularly sensitive components. We propose a scenario where the Mobile Operator Application server communicates with the device resident component of the *Security Agent*. This subsequently uses the security services provided by the secure entity to establish authenticated keys.

In section 2 we review the design requirements for a Security Agent deployed on a GSM/3GPP Mobile Station. In section 3 we review our proposed authenticated key establishment scheme. A protocol for wireless installation of the Security Agent to a compatible but remote and unprepared Mobile Station (colloquially termed "OTA" and "backward compatible field installation") is detailed in section 4, whilst the protocol used to establish session integrity and confidentiality keys is presented in section 5. Finally, in section 6, we describe the Proof of Concept model constructed using readily available components and open source development tool kits and provide concluding remarks in section 7.

# 2 Design Requirements

A critical requirement is for a backward compatible field installable *Security Agent* designed to provide an authentication service using SIM based credentials. It is required to be executable on a significant proportion of globally standardised and deployed Mobile Stations. The design of our proposed *Security Agent* uses four widely adopted technologies and standards:

- ETSI TS03.48 Security Mechanism [1];

- SIM Application Toolkit (SAT) [12];

- MIDP2.0 J2ME Runtime Environment [15];

- UICC Java Card SIM cards [3].

## 2.1 ETSI TS03.48 Security Mechanism

ETSI TS03.48 [1] specifies a mechanism for providing end to end security for any Short Message Service (SMS) going to or from the SIM card. SMS messages contain a maximum of 140 bytes. SMS messages are sent in accordance with the SUBMIT\_SMS format, and received with the SMS\_DELIVER format. Translation from one format to the other is performed by the Short Message Service Centre (SMSC), an active component of the network. In an output SUB-MIT\_SMS packet, the 40 bytes of User Data are complemented by a 13 byte *Mandatory Header* and an optional variable length *User Data Header*.

- The Mandatory Header includes the Data Coding Scheme byte which specifies how the data is encoded, and the Protocol Identifier byte which specifies how the receiving mobile should process the message. One of these values, 0xF7, specifies that the device should pass the whole packet to the SIM card.

- The User Data Header comprises a concatenation of tag, length and value (TLV) fields which describe the optional features that should be applied to the attached 140 bytes of user data. Of interest to our proposal are tag values 0x00 and 0x70, meaning Concatenated SMS and SAT Security respectively.

- The concatenated SMS tag allows up to 255 SMSs to be concatenated. It is reported [13] that most operators limit this to approximately five, because of uncertain and indeterminate device operation when receiving larger numbers of SMS messages to be concatenated. Five messages represents a total payload of 5x140 = 700 bytes [18].

- The presence of the SAT Security tag (0x70) indicates that the message contains an additional header, the *Command Header*, prior to the *User Data Header*. This comprises of 9 fields which define how the User Data is secured by:

- \* specifying the cryptographic functions,

- \* providing a replay protection counter,

- \* quoting the sender's cryptographic integrity value for the secured User Data Header.

Through the use of this SAT Security mechanism it is possible to provide confidentiality and integrity services for up to 700 bytes of user data, when the data is sent between the Mobile Operator application server and the SIM card. Performance and payload are limited and applications are restricted.

#### 2.2 SIM Application Toolkit

The SAT API allows an application on the SIM card to be informed of events by, and to issue commands to, the host mobile device. When an information flow is initiated to the SIM application, it is termed an event download, and when an information flow is initiated from the SIM application it is termed a proactive command. Using the proactive command SET\_UP\_EVENT\_LIST, the SIM application can register to be informed of a number of events via the ISO/IEC 7816-4 ENVELOPE APDU command [8]. Of relevance to this paper is the SMS\_PP or CELL\_BROADCAST event, which downloads the contents of the received SMS to the SIM application as a compound TLV in the data field of an ENVELOPE APDU [13]. The SIM application's response to the ENVELOPE command is then returned to the sender in a response packet.

#### 2.3 MIDP2.0 J2ME Runtime Environment

A Java application that runs on a Mobile Information Device Profile (MIDP) 2.0 device is known as a MIDlet and may be installed within a certain domain if

it complies with the domain-specific access control requirements [6]. There are 4 domains specified for GSM compliant devices:

- Untrusted,

- Trusted 3rd Party,

- Mobile Operator,

- Manufacturer.

A Domain Protection Root Certificate (DPRC) controls MIDlet access to a domain. The DPRC must be made available at a specified location in the SIM application [15]. The MExE [2] security framework, when making an access control decision relies on signature verification of the signed MIDlet using the public key contained within the DPRC. Successful verification of the digital signature allows the MIDlet to be installed into the appropriate domain of the device.

Any MIDlet within a domain enjoys a set of unique permissions provided by that domain. The permission model allows these installed MIDlets access to restricted and sensitive APIs. The Security and Trust Services API [16] specifies that access to three of the four defined packages is limited to MIDlets located within the operator domain. These packages are:

- SATSA-APDU

- SATSA-JCRMI

- SATSA–PKI

These provide the ability for MIDlets to access trusted elements (i.e. a SIM card) using APDU communication, invoke a method of a remote Java Card object and provide support for digital signatures and credential management. It is worth nothing the value of being able to process cryptographic functions upon the device, as well as the smart card, as the card is a constricted environment [19].

#### 2.4 UICC Java Card SIM Cards

The Global Platform specification [10] is the industry standard interface for downloading applications and is the most important international specification for application management in multi-application smart cards [11, 21]. This standard allows card issuers to securely manage third party applications independently of the operating system provider. Mobile Operator are increasingly deploying UICC [3] Java Cards, where the SIM application [4] is just one of the possible java applications [9] that the card is capable of running. Java applications that run on smart cards are known as Applets. A Card Manager is responsible for ensuring that new Applets are integrity checked and their source authenticated prior to installation. This security service uses a secret key,  $K_{CI}$ that is embedded in the smart card prior to issue and termed the Card Issuer Key. Although a UICC SIM card can execute multiple Applets from different providers, the Card Manager application will be owned by the Mobile Operator who actually owns and issued the physical card.

## 3 The Proposed Scheme

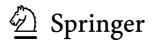

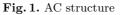

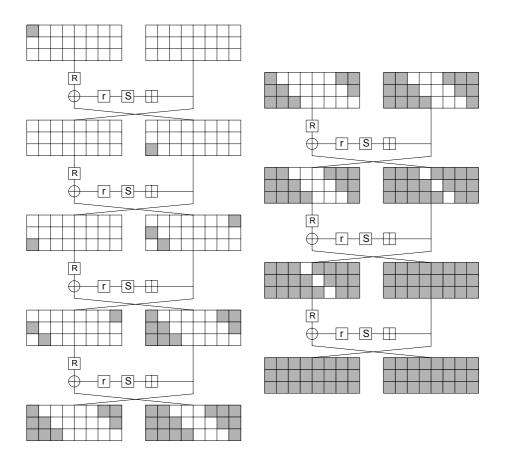

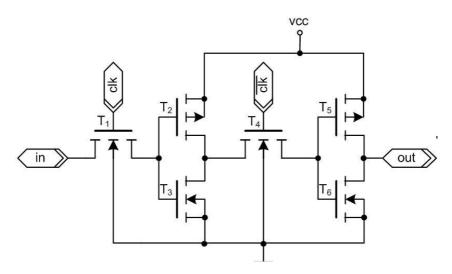

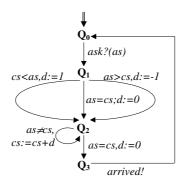

Consider the scenario of having the requirement to remotely deploy our *Security Agent* to Mobile Stations in the field. The device is capable but unprepared; this section introduces the proposed scheme to install the *Security Agent*. This is again described as a protocol in section 4 and is represented in Fig. 1. The scheme is preparation for the execution protocol, detailed in section 5 that establishes session keys for future communication.

- 1. A small SAT application is securely installed OTA to the SIM using the TS03.48 mechanism.

- 2. The SAT application uses the proactive command SET\_UP\_EVENT\_LIST to register to be informed, via the ISO/IEC 7816-4 ENVELOPE APDU command [8], when a SMS\_PP or CELL\_BROADCAST event occurs.

- 3. A corresponding SMS\_PP or CELL\_BROADCAST is sent to the device. The DPRC is contained within the payload of a of the concatenated SMS messages.

- 4. The device transfers the payload to the SAT application as a compound TLV in the data field of an ENVELOPE APDU command. The DPRC is stored in the appropriate location of the UICC SIM Card [15].

- 5. The SAT application retrieves the SIM's unique identifier, and returns it to the device as the response to the ENVELOPE command.

- 6. The unique identifier is then returned to the Mobile Operator application server. This acts as a proof of delivery of the DPRC and enables the Mobile Operator application server to reference the card's secret key  $K_{CI}$  and commence the MIDlet preparation and download process.

- 7. Using the SIM's unique identifier, the Mobile Operator constructs the appropriate *Security Agent* MIDlet containing the relevant install commands and

Fig. 1. Installation Scheme

6

byte code for the Security Agent Applet. The Applet byte code is encrypted and digested with the card issuer key  $K_{CI}$  and packaged within the MIDlet JAR file.

The MIDlet must be prepared for the secure MIDlet installation procedure defined by J2ME MIDP2.0 and implements a second security context between server and device. The server generates a RSA X.509(v3) certificate or requests one from a Certificate Authority (CA). The certificate is inserted into the application descriptor of the MIDlet application. The path of the descriptor holds all certificates necessary to validate the application except the root certificate. The DPRC resides on the smart card and is called into play during MIDlet installation. Finally, the signature of the JAR file (format used to distribute MIDlets) is generated with the private key of the RSA certificate according to the EMSA-PKCS-v1\_5 encoding method of PCKS#1 version 2.0 standard. This signature is then inserted into the application descriptor, the MIDlet is considered prepared and delivered to the device.

The J2ME JRE must authenticate the MIDlet application for installation into a secure domain. First the certificate is retrieved from the application descriptor and validated against the DPRC held upon the smart card. The JRE then verifies the MIDlet JAR file; by taking the public key from the verified signer certificate along with a fresh SHA-1 digest of the JAR file and comparing it to signature defined in the application descriptor. The JRE can install the MIDlet into the Operator domain of the MIDP2.0 runtime environment.

- 8. The Security Agent MIDlet is installed in the Operator domain of the user device with full access to JSR 177 APIs. This allows APDU commands to be issued to SIM card. The Security Agent MIDlet executes its Applet installation routine. The MIDlet starts by using the SELECT command to initiate communication with the SIM Card Manager. Once the Card Manager application is selected the MIDlet then issues a GET CHALLENGE command.

- 9. Before the Card Manager will accept installation of an Applet onto the SIM Card, it must first authenticate the source of the Applet. It does this by responding to the GET CHALLENGE with a random number  $r_C$ .

- 10. The MIDlet is not in possession of the secret  $K_{CI}$  required to prove a trusted source for a new Applet, so the challenge response  $r_C$  must be sent back to the Server.

- 11. The Server encrypts  $K_{CI}$  and  $r_C$  with  $K_{CI}$  and returns the byte string to the MIDlet.

- 12. The MIDlet authenticates the source of the applet using the EXTERNAL AUTHENTICATE command providing the encrypted response to the random challenge  $r_C$ . The Card Manager, also in possession of  $K_{CI}$ , authenticates the source of the Applet and allows the applet installation process to continue.

- 13. The Security Agent MIDlet now transfers the encrypted and integrity protected byte code of the Security Agent Applet to the SIM card via the ENVELOPE command. At no point does the MIDlet have any knowledge of the key  $K_{CI}$  as it acts as a delivery mechanism between SIM and Server for predefined parcels of bytes. The integrity and confidentiality of the applet code and the long term secret  $K_{CI}$  is assured. Subsequent to the download-

ing of the byte code to the card, the same Card Manager using, the Global Platform specified Data Authentication Pattern (DAP) verifies the integrity of the received byte code. Verification allows the byte code to be decrypted. A *Security Agent* applet instance is created and registered with the Java Card runtime environment.

Contained within the Security Agent Applet byte code is a long term Security Agent symmetric key  $K_{SC}$  used for mutual authentication and establishment of secure session keys for subsequent execution of a Security Agent controlled authenticated key establishment process (Section 5).

14. APDU communication between the MIDlet and Applet components of the *Security Agent* can now proceed under J2ME application control. Communication between the Application Server and the J2ME environment may use any of the supported network protocols such as http or https for security services.

#### 4 Installation Protocol

Our protocol uses both symmetric and asymmetric cryptographic techniques [20] to provide the authentication and integrity services required. The specific algorithms involved are either defined by the standards or rely on what the individual smart card supports.

Throughout this discussion we will use the following notation:

$$S = \text{Server}$$

$$M = \text{MIDlet}$$

$$C = \text{SIM card}$$

where:

$K_{CI}$  = Shared secret between Server and SIM pre-issuance

$K_{SC}$  = Shared secret between Server and SIM post-installation

$\operatorname{Cert}_{DPRC}$  = Domain Protection Root Certification

$PK = Public \text{ key of } Cert_{DPRC}$

$\epsilon_K(D) =$  Symmetric encryption of data D using key K

$S_K(D) =$  Signature computed on data D using key K

$MAC_K(D) = MAC$  computed on data D using secret key K

$r_E$  = Random nonce generated by entity E (S, C or M)

$i_E$  = Identifier of entity E (S, C or M)

CK = Cipher Key

IK =Integrity Key

APDU() = APDU command from MIDlet to SIM card

SAT() = GSM SAT communication mechanism

SMS() = SMS communication mechanism

#### **PHASE 1.** Install the MIDlet into the Operator Domain.

$$S \to C: SAT(MAC\_ID)$$

(1)

$$S \to C: SAT(SAT Applet Install \ code)$$

(2)

$$S \to M: SMS(Cert_{DPRC})$$

(3)

$$M \to C: APDU(\text{ENVELOPE}: Cert_{DPRC})$$

(4)

$$C \to M: APDU(\text{ENVELOPE}: UID)$$

(5)

$$M \to S: SMS(UID)$$

(6)

$$S \to M : S_{PK}(MIDlet) \| (MIDlet)$$

$$\tag{7}$$

Our protocol has been designed on the assumption that the device and SIM card are preissued and in the field, and although they are both capable, neither are prepared nor contain preinstalled application code to create the desired secure high bandwidth channel. The first step is to therefore prepare the SIM card so that the MIDlet can be installed within the Operator domain of the J2ME device. It is assumed, however, that the device is operational on the Operators network (i.e. user authentication and sign on to the network has successfully been performed by the AUTHENTICATE [4] and subsequent functions of the 3GPP challenge response mechanism [24]). Although messages (1) through to (3) are unidirectional from the Server to the SIM card or mobile, we have presented them as 3 individual protocol messages. This is because they are transferred using GSM standard 03.48 and are most likely sent as 3 independent SMS messages. Protocol messages (1) provides the SIM card with the identifier specifying which GSM standard 03.48 MAC algorithm will be used to confirm integrity and data origin throughout the protocol sequence. Message (2) provides the SAT code be installed upon the card, whilst message (3) provides the root certificate of the device J2ME Operator domain. The payload of these messages are stored in the SIM card. The role of the SAT code is to discover the card's unique identifier (UID). By the means of the same mechanism the UID of the SIM card and  $r_C$  is securely sent back to the Server. This information is used to find the related  $K_{CI}$ , this key is used to encrypt and sign the Security Agent Applet byte code that is embedded and readied for delivery as part of the integral code that comprises the MIDlet.

Upon receipt of protocol message (7), the MExE [2] J2ME implementation on the client will verify the signature using the root certificate on  $\text{Cert}_{DPRC}$  previously stored into the SIM card via message (3). Valid verification provides data origin authentication and integrity of the MIDlet JAD and JAR files received. The *Security Agent* MIDlet is now installed OTA in the Operator domain of the J2ME MIDP2.0 compliant implementation of the client device, with full permissions to utilise SATSA-APDU and SATSA-PKI packages defined by JSR 177.

**PHASE 2.** Install the Applet into the SIM card

$$M \to C$$

: APDU(SELECT: AID<sub>CM</sub>) (8)

$$M \to C$$

: APDU(GET CHALLENGE) (9)

$$C \to M$$

: APDU $(r_C)$  (10)

$$M \to S$$

: SMS $(r_C)$

$$S \to M$$

: SMS $(\epsilon_{K_{CI}}(K_{CI} || r_C))$  (12)

$$M \to C$$

: APDU(EXTERNAL AUTHENTICATE:  $\epsilon_{K_{CI}}(K_{CI} || r_C)$  (13)

$$M \to C$$

: APDU(MAC<sub>KCI</sub>(Applet)  $\|\epsilon_{KCI}(APPLET))$  (14)

$$M \to C$$

: APDU(INSTALL(Install): AID<sub>SA</sub>) (15)

$$M \to C$$

: APDU(INSTALL(Selectable): AID<sub>SA</sub>) (16)

The MIDlet, now securely stored OTA in the device, carried an array of byte codes (see appendix 2). These byte codes represent an encrypted and signed CAP file from the Server using the shared secret between the SIM and Server,  $K_{CI}$ . The process of verifying the MIDlet during download and installation, using Cert<sub>DPRC</sub>, has already verified the integrity of these byte codes as well as the MIDlet application. The steps (8) to (16) outline the process going on between device and card but the untrusted device would have no knowledge of what is being sent as it is protected by a secret that it is not privy to.

Step (8) sends the SELECT command to the card to communicate with the Card Manager on the SIM operating system that will handle the authentication of the card acceptance device. This authentication process is represented by steps (9) to (13), it begin with collecting a challenge, random number, from the card using the GET CHALLENGE commands. This challenge is packaged in an SMS, step (11), and sent back to the Server. The Server using its shared secret  $K_{CI}$ , encrypts the number along with the key itself and sends it back to the MIDlet (12). The final authentication is performed by the Global Platform EXTERNAL AUTHENTICATE command which holds the encrypted challenge response (13). AID<sub>SA</sub> refers to the unique application identifier of the Security Agent Applet. Once authenticated, steps (14) through (16) show the encrypted and signed download of Security Agent Applet to card, it's subsequent installation and final completion of the process allowing it to be selected by any Operator Domain located MIDlets.

The MIDlet pseudo code to generate this secure authentication, download and installation of *Security Agent* Applet to SIM from an untrusted device is presented in appendix 1.

#### 5 Execution Protocol

At some time later, i.e. after the http session of PHASE 2 has closed, the Operator may choose to download bulk data securely from the Server to the SIM card. Before this can begin both endpoints must verify the identity of the other with a mutual entity authentication protocol. We take our authentication protocol from the ISO/IEC 9798 standard [14], deriving session keys for data origin authentication, data integrity and data confidentiality as part of our authenticated key establishment protocol. The choice of protocol is heavily influenced by the parameters and characteristics of our mobile environment. For similar

(11)

reasons, as stated previously, authentication via symmetric cryptography is preferred, and a MAC based approach limits the amount of network traffic required to a minimum. The choice is further restricted owing to the time-less nature of the SIM card [21]. Only three possible sources of time are available; an internal clock, a remote server or a neighbouring device [22] and there are no other alternatives. To have an internal time keeper would require at least a portion of the card chip to have a source of permanent power [7]. Although it is, of course, possible for the SIM card to obtain a measure of time from the client device via the TIMER MANAGEMENT proactive command and TIMER EXPIRATION event download of the SAT API. The client device is, as stated previously, likely to be untrusted by Operators for any function concerning the communication of potentially network critical information, and cannot be used as a source of time for confirming message freshness. In consequence message timeliness, to protect against replay attacks, must be achieved with either logical time stamps or nounces. In conclusion, therefore we have adopted the three-pass mutual authentication protocol using MACs and nounces as specified in ISO/IEC 9798-4 clause 5.2.2.

#### **PHASE 3.** Perform mutual entity authentication

$$S \to M$$

: start MIDlet with push registry (17)

$M \to C$ : APDU(select Applet) (18)

$$C \to M$$

: APDU $(r_C)$  (19)

- $M \to S: r_C$  (20)

- $S \to M: i_S ||i_C|| r_C ||r_S|| \mathrm{MAC}_{K_{SC}}(i_S ||i_C|| r_C ||r_S)$  (21)

$$M \to C: \operatorname{APDU}(i_S ||i_C|| r_C || r_S || \operatorname{MAC}_{K_{SC}}(i_S ||i_C|| r_C || r_S))$$

(22)

$$C \to M$$

: APDU $(i_C || r_S || MAC_{K_{SC}}(i_C || r_S))$  (23)

$$M \to S: \ i_C \| r_S \| \operatorname{MAC}_{K_{SC}}(r_S \| r_C) \tag{24}$$

Once again this step starts with an invocation of the push registry via message (17) and the device MIDlet Security Agent loaded in (7) selecting the SIM Applet loaded following message (16). The SIM card Applet generates a random nounce  $r_{C}$ , stores it, and supplies it to the MIDlet (19) where it is passed on (without storing) to the Server (20). Server generates nounce  $r_S$ , stores it together with received nounce  $r_C$  and responds with (21). Again this is passed through the MIDlet to the SIM card Applet via an APDU, message (22). Upon receipt the SIM card Applet verifies that the received  $r_C$  is the same as the one sent in (19) and that the identifiers are correct (note the UID could be used for  $i_C$ and a parameter of certificate  $Cert_{DPRC}$  supplied to the SIM card via message (3) used for  $i_S$ ). The SIM card Applet then recalculates the MAC and if correct accepts the Server. Now that the Server is authenticated to the SIM card Applet, then Applet responds with message (23) via the MIDlet, which again passes it straight through to the Server in message (24). When Server receives message (24) it checks that the received value  $r_S$  is indeed the one sent in (21) and that the SIM card identifier  $i_B$  is correct. After confirming the MAC calculation the Server can then accept the SIM card Applet as valid. Following the mutual entity authentication of STEP 3, both Server and SIM card will establish Integrity IK and Confidentiality CK keys to protect the subsequent bulk data exchange between the Server and the SIM Card.

PHASE 4. Set up session keys to protect the content to be downloaded

$$CK = f1_{K_{SC}}(r_S || r_C) \tag{25}$$

$$IK = f 2_{K_{SC}}(r_S || r_C)$$

(26)

Both Server and SIM card Applet will contain identical functions f1 and f2 to calculate the session cipher and integrity keys using the protocol nounces  $r_S$  and  $r_C$  and the long term shared secret  $K_{SC}$ . Now that session keys have been established the bulk data may be transferred to the SIM card encrypted for confidentiality with CK and concatenated with a MAC using IK for data origin authentication and integrity as necessary for the data being transferred.

# 6 Proof of Concept Model

To validate our proposal we constructed a proof of concept model, based on readily available open source tools; it comprised of:

- Server:

A J2EE Servlet web application performed the Mobile Operator function and was packaged as a Web Application Archive (WAR) file for easy deployment on a Tomcat Apache Web Server.

- Mobile Device:

The J2ME Client was emulated by the Wireless KToolbar [23] from Sun Microsystems and run our *Security Agent* MIDP 2.0 MIDlet on the reference J2ME implementation.

- SIM card:

The SIM card Security Agent function was provided by a Gemplus GemXpresso smart card. This was a Java Card and adhered to a number of industry standards such as Global Platform and had on-card cryptographic capability. The equipment used to connect the card to the test-bed was a USB card reader and Gemplus RAD3 development environment was used in early tests to load Security Agent Applets. This could have been just as easily realised using a variety of different platforms, notably G&D development hardware and tools.

The demonstration environment for our model was implemented in J2SE. J2SE provides the necessary Java Swing classes for monitoring the various use case applications being tested. The model is designed so that each phase of a specific use case is initiated manually and monitored by visual feedback through the use of J2SE's GUI LayoutManager class and ActionListener interface.

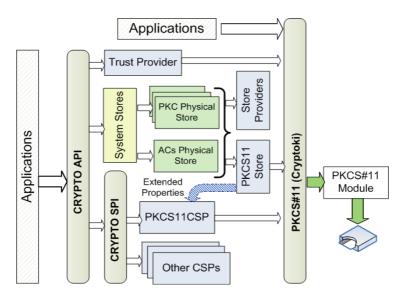

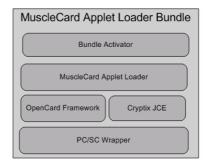

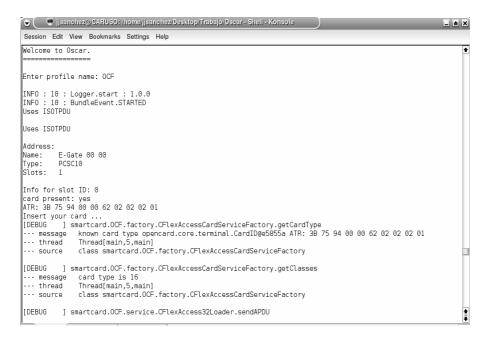

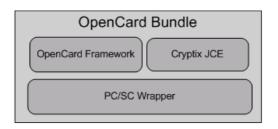

There are different technologies involved in this scenario and as such only some aspects of the system could be placed within the scope of the practical work undertaken. The SAT application download process is well document and involves access to SMS generation so this was omitted. The MIDlet could be constructed and the communication between the server and MIDlet over a secure channel was considered within the scope of this work and practically demonstrated using a secure HTTP link between a web server and mobile device. Both entities employed Java based technologies and demonstrated a secure channel based upon mutual authentication with a shared secret. The cryptographic functionality involved could not be performed by the MIDlet as the SATSA-PKI and SATSA-CRYPTO packages are provided by the JSR-177 and at the time of investigation was unavailable. Our approach was to separate out this functionality to a J2SE application that would communicate with the MIDlet and in turn generate APDU commands to the smart card whilst perform any cryptographic functions required. This allowed the JSR-177 to be effectively modelled with only a moderate increase in complexity. The J2SE JSR-177 proxy used the Open Card Framework (OCF) to create a connection to the smart card and build command and response APDU for exchanges in data.

# 7 Conclusion

In this work we introduce a methodology, discuss the component technologies and define a protocol for establishing a security context between a Mobile Operator application and SIM card. A solution is proposed to establish a *Security Agent* on an untrusted mobile device and trusted SIM card using "Over The Air" (OTA) techniques. A proof of concept demonstration capability is implemented with example java source code presented.

This work creates confidentiality and integrity session keys, CK and IK respectively. These are independent off all network security keys and therefore eligible to protect unrelated data, e.g. value added applications. The extension of trust from inherent network related credentials, to independent credentials used solely for providing security services to post-purchase applications, is an important step towards fulfilling the true potential of the mobile station field base by executing a new generation of secure applications.

# Acknowledgements

We would like to extend appreciation to Chris Mitchell for early guidance and participation. Additionally, thanks to Jennifer Squire for patience whilst proof reading drafts.

# References

- 3GPP TS 03.48. Technical Specification Group Terminals; Security Mechanisms for the SIM Application Toolkit; stage 2. http://www.3gpp.org, 2001.

- 3GPP TS 23.057. Technical Specification Group Terminals; Mobile Execution Environment (MExE); Functional description; Stage 2. http://www.3gpp.org, 2003.

- 3GPP TS 31.101. Technical Specification Group Terminals; UICC-terminal interface; Physical and logical characteristics. http://www.3gpp.org, 2003.

- 3GPP TS 31.102. Technical Specification Group Terminals; Characteristics of the USIM application. http://www.3gpp.org, 2003.

- R. Anderson and M. Kuhn. Tamper resistance a cautionary note. In *The Second USENIX Workshop on Electronic Commerce Proceedings, Oakland, California*, pages 1–11. USENIX Association, November 1996. http://citeseer.ist.psu.edu/ 400120.html.

- C. Block and A. C. Wagner. MIDP 2.0 Style Guide. The Java Series. Addison-Wesley, London, 2003.

- V. Cordonnier, A. Watson, and S. Nemchenko. Time as an aid to improving security in smart cards. In 7th Annual Working Conference on Information Security Management and Small Systems Security, pages 131–144. Kluwer Academic Press, London, 1999. Amsterdam, The Netherlands.

- ETSI TS 100 977. Digital cellular telecommunications system(Phase 2+); Specification of the Subscriber Identity Module Mobile Equipment (SIM-ME) Interface. ETSI, http://www.etsi.org, 2000.

- ETSI TS 101 476. Digital cellular telecommunication system (Phase 2+); Subscriber Identity Module Application Programming Interface (SIM API); SIM API for Java Card; Stage 2 (GSM 03.19). ETSI, http://www.etsi.org, 2000.

- 10. Global Platform. Card Specification v2.1.1. http://www.globalplatform.org, 2003.

- GSM 03.19, Version 8.2.0. Digital Cellular Telecommunications System (Phase 2+); Subscriber Identity Module Application Programming Interface (SIM API); AIM API for Java Card; Stage 2. ETSI, http://www.etsi.org, 2001.

- GSM 11.14. Digital cellular telecomunications system (Phase2+); Specification of the SIM Application Toolkit for the Subscriber Identity Module-Mobile Equipment (SIM-ME) interface. ETSI, http://www.etsi.org, 2001.

- S. B. Guthery and M. J. Cronin. Mobile Application Development with SMS & the SIM Toolkit; Building Smart Phone Applications. McGraw-Hill, 2002.

- ISO/IEC 9798-4. Information technology Security Techniques Entity Authentication - Part 4: Mechanisms using a cryptographic check function 2nd ed., http://www.iso.org, 2nd edition, 1999.

- JSR-118 JCP. Mobile Information Device Profile, v2.0 (JSR-118). Sun Microsystems, http://java.sun.com, 2002.

- JSR-177 JCP. Security & Trust Services API (SATSA) (JSR-177). Sun Microsystems, http://java.sun.com, 2004.

- J. A. MacDonald and C. J. Mitchell. Using the GSM/UMTS SIM to secure web services. In 2nd IEEE International Workshop on Mobile Commerce & Services (WMCS). IEEE, IEEE Computer Society Press, July 2005. Munich, Germany.

- 18. J. A. MacDonald, W. G. Sirett, and C. J. Mitchell. Overcoming channel bandwidth constraints in secure SIM applications. In R. Sasaki, S. Qing, E. Okamoto, and H. Yoshiura, editors, 20th IFIP International Information Security Conference (SEC 2005) - Small Systems Security and Smart cards,, volume 181 of IFIP International Federation for Information Processing. Springer Science and Business Media, May 2005. Chiba, Japan.

- K. Markantonakis. Is the performance of the cryptographic functions the real bottleneck? In M. Dupuy and P. Paradinas, editors, *Trusted Information: The New Decade Challenge*, IFIP TC11 16th International Conference on Information Security (IFIP/SEC'01) June 11-13, pages 77–92. Kluwer Academic Publishers, 2001. Paris, France.

- F. Piper and S. Murphy. Cryptography A Very Short Introduction. Oxford University Press, 2002.

- W. Rankl and W. Effing. Smart Card Handbook. John Wiley & Sons, Ltd, 3rd edition, 2003.

- 22. L. Rousseau. Secure time in a portable device. Proceedings of 3rd Gemplus Developer Conference, Paris, France, 2001. Gemplus.

- Sun Wireless Toolkit. Wireless Toolkit, Version 2.1,. Sun Microsystems, http://java.sun.com/products/j2mewtoolkit, 2004.

- M. Walker and T. Wright. GSM and UMTS: The creation of global mobile communications. John Wiley & Sons, Ltd., 2002.

#### A Appendix 1 – Psuedo Java Code

This pseudo code is intended to be a demonstration of the proposed method of embedding encrypted Security Agent Applet code within the body of the Security Agent MIDlet. The MIDlet can call the Install method of a packaged class called Secure\_Applet and undertake the selection of the Card Manager, authentication of shared secret, downloading of CAP file, its installation and finalisation without actually exposing the underlying Operator secret to the MIDlet. The Security Agent Applet is encrypted within the MIDlet and its integrity is checked on-card during installation.

The following code is not intended to be a literal but uses Java based concepts to express the intention of the proposal. The aim is to illustrate the declaration of a two dimensional array; a primary array holding arrays of 255 bytes representing APDU commands. The concept is that these APDUs can be declared by the Server during preparation of the MIDlet and therefore the device would not have the opportunity to alter or access the information. The only function the device or MIDlet must perform is the act of sending the APDUs to the device.

```

public class Secure_Applet {

1

\mathbf{2}

//-- ISO7816 offsets

private bINS = ISO7816.OFFSET_INS;

3

private bCLA = ISO7816.OFFSET_CLA;

4

private bP1

= ISO7816.OFFSET_P1;

5

private bP2

= ISO7816.OFFSET_P2

6

private bLC = ISO1716.OFFSET_LC;

7

private bData = IS07816.OFFSET_CDATA;

8

9

10

//--array of APDU byte codes

11

private byte [9] [255] baAC

12

//-- select AID

= \{00 \text{ A}4 04 00 07 \text{ A}0 00 00 00 18 43 4D\},\

13

14

15

//-- External Authenticate

{84 82 03 00 10 40 2F 82 CE 30 2C F5 78 F7 F7 60 32 0B 5A 4F 0E},

16

17

//-- First APDU of CAP file load

18

19

{84 E6 02 00 20 39 B0 DB 15 04 8D 75 BC 8D 71 46 83 52 A8 E2 D2

7D 48 32 25 AD DF DC 44 E2 28 55 2D 83 31 8B 34 00},

20

21

22

//-- following data packets

{84 E8 00 00 D8 B0 23 9E 36 52 BF 40 03 A1 F1 43 D8 3D 6A F8 93

23

24

//--consider full 255 byte apdu data array

25

71 OC 6D B3 41 56 B8 09 84 71 7C},

26

\{\ldots\},\{\ldots\},\{\ldots\},\{\ldots\},\{\ldots\},\{\ldots\},\{\ldots\}\};

27

28

public installSecureApplet() {

29

try {

//-- create card service and connect

30

31

//-- send all APDU commands confirming

//-- for length of parent array loop

32

for (int x=0; x < baAB.length; x++){

33

34

//-- build APDU object using array and offsets

35

cmdAPDU = new ISOCommandAPDU(

36

baAC[x][bINS], baAC[x][bCLA], baAC[x][bP1],

baAC[x][bP2], baAC[x][bData];

37

//-- send APDU and catch response.

38

39

resAPDU = service.sendCommandAPDU(cmdAPDU);

if (Integer.toHexString(resAPDU.sw()) != "90_00"){

40

break:}}

41

//--catch errors and close down all objects}}

42

```

Listing 1.1. Psuedo MIDlet code

# Towards a Secure and Practical Multifunctional Smart Card

Idir Bakdi

Lehrstuhl für Wirtschaftsinformatik II, Universität Regensburg, 93040 Regensburg, Germany idir.bakdi@wiwi.uni-regensburg.de

Abstract. One of the most promising features of smart card technology is its potential to serve several applications using a single hardware token. Existing multifunctional smart cards, however, are either simple and suffer from serious limitations or they have a high complexity that is not justified for most applications. This paper describes a new scheme permitting different applications to flexibly share a hardware token. The proposed solution supports off-line transactions as well as post-issuance loading. Each application can load one or more "virtual tokens" (remotely) into a common smart card. Despite its simplicity, the scheme guarantees the authenticity and integrity of virtual tokens and prevents their duplication. Moreover, it protects the privacy of card holders by providing a possibility to use pseudonymous identities that cannot be linked to one another.

Keywords: Multifunctional smart card; secure hardware token; privacy.

## 1 Introduction

Nowadays, we all carry a lot of tokens in our pockets. These are keys, magnetic stripe cards, smart cards, tickets, etc. Each application has to implement its own infrastructure to issue and subsequently use these tokens. From an ergonomic as well as from an economic point of view, it would be beneficial to virtualize all those tokens, i.e. to convert them into digital files that can be loaded onto a single medium. However, as most tokens are critical for the security of the applications they serve, one cannot just load their virtual counterparts on a storage medium such as a floppy disk. On the one hand, such a medium would not offer any protection against misuse in case it gets lost or stolen. On the other hand, a virtual token could be copied at will as it can be read by anyone holding the medium. One possibility to overcome these difficulties is to use a microchip as implemented on smart cards to hold the files representing tokens. This way, they are protected both against misuse by someone else than the legitimate user and against unauthorized duplication by the holder himself. This paper describes a new scheme that uses such a chip to realize a secure and practical multifunctional token.

The remainder of this paper is organized as follows. After a short review of existing solutions and their most serious shortcomings in the next section,

<sup>©</sup> IFIP International Federation for Information Processing 2006

the main security requirements of a multifunctional smart card are outlined in section 3. Section 4 contains a description of the new approach. Finally, the last section is devoted to some conclusions summarizing this work.

## 2 State of the Art

The idea of using a single token for multiple purposes is quite an old one. Its simplest and most famous implementation is perhaps that of a master key able to open several locks. Recently, many solutions appeared which aim at grouping many applications on a single smart card, or more generally, on a single microchip. Most of them can be categorized into one of two classes. The first class, denoted by *single ID cards* in this paper, is the simpler one. So called *multi-application smart cards* constitute the second class. They are more comprehensive and consequently more complex than single ID cards. In the following, these two classes are described in more detail sketching their pros and cons.

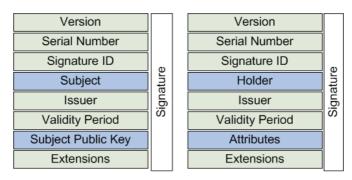

#### 2.1 Single ID Cards

The simplest realization of a single ID card is to have a number (an ID) that uniquely identifies a person across several back-end systems stored on a smart card. Each system keeps its own set of data associated with a given user in its central database. The smart card merely serves as a reference to that account. As all systems share the same number for a given user, a single card suffices to identify him in all of them. Put another way, single ID cards realize an authentication by possession of a person already known to the different systems through a common identification scheme. A more advanced version of this solution uses smart cards capable of producing digital signatures. The idea is to have the user's private key stored on his card, whereas the corresponding public key is shared by all participating back-end systems. The main advantages and drawbacks of this class are presented in the following.

#### Advantages

**Simplicity:** Solutions built on single ID cards are very simple. A single ID card merely identifies a person. Each application maps the ID to a data set associated with the corresponding user. The management of relevant application data is thus differed from the card to the more powerful back-end systems, which facilitates implementation.

**Generic Digital Signature:** In case a digital signature card is used, the card can additionally be used to digitally sign electronic documents. Thus, a large category of applications requiring the authenticity and non-repudiation of electronic documents can be covered. Many countries already have laws that guarantee to certain kinds of digital signatures a legal status equivalent to that of a classical (i.e. manual) signature.

## Drawbacks

No Off-Line Functionality: As the card merely represents a pointer to a data set stored in the back-end system, it can only be used given an online access to the central database. This is especially difficult when the verifier does not belong to the issuer's organization. To verify a student card, an employee sitting at the entrance of a cinema would have to access data from the student office of the corresponding university.

**Privacy Concerns:** As all the back-end systems use the same ID, comprehensive user profiles can be easily constructed by matching the different data sets belonging to a person. This raises privacy concerns because of possible misuse.

**Single Point of Failure:** The different back-end systems all rely on a unique ID per user which is tightly bound to a single card. If this hardware token is lost, stolen, or compromised, all those systems are affected at once. That is, the card holder has no possibility to mitigate the risk resulting from a loss or theft by employing more than one smart card.

**High Demands:** In case a signature card is used, the requirements concerning the card's protection and the key management are very high. This makes sense when the card is used to generate legally recoverable digital signatures. For most use cases, however, such functionality is not needed. A train conductor only has to be convinced that a passenger possesses a valid ticket. He does not need to get the traveller's legally recoverable signature. In such cases, high demands would unnecessarily burden the solution.

## 2.2 Multi-application Smart Cards

This class employs so called *multi-application card operating systems (MACOS)* [14, p. 308] which try, in analogy to computer operating systems, to abstract the underlying hardware in order to make it possible for different applications to run on it. They offer an application programmer interface (API) that can be used to access the card's services. The newer MACOS (e.g. MULTOS [9] or Java Card [19] [8] [5]) do not only provide for the hosting of many applications on the same microprocessor, but also make it possible for the same application to run on different chips by employing a virtual machine. Using the Java Card platform for instance, each system can load its applet (a small application written in Java) on the card where it can be executed together with other applets. In the remainder of this section, the main advantage of multi-application smart cards as well as their drawbacks are discussed.

# Advantage

**Universality:** The vision of multi-application smart cards is to have a universal chip able to execute arbitrary code. That is to say, the goal consists in the miniaturization of multi-purpose devices such as personal computers or handhelds. This would enable everyone to write applications that do whatever he

wants and load them to be executed on card. The employed smart card would bear all the necessary functionality and would not need to rely on any back-end system, thus providing a high level of flexibility and autonomy.

## Drawbacks

**Complexity:** Due to their complexity these systems are far from being mature. This results in the following limitations of current solutions.

- The capabilities of MACOS are restricted due to limitations in processing performance and storage capacities of the underlying hardware. It will take some time before they reach the universality of operating systems running nowadays on personal computers, for instance.

- Many of the current solutions do not offer the possibility of post-issuance loading. The applications are installed on the card before the latter is issued. This is for instance the case when using MULTOS [12]. Java applets can be loaded after the card is issued, but until version 2.2 of the Java Card specification there was no possibility to remove already loaded applets. This shows the kind of difficulties encountered in practice.

Security: The main advantage of multi-application smart cards, consisting in their ability to host arbitrary applications and to execute their code, constitutes at the same time a considerable security risk. Some applications running on the card may not be trusted. They could access sensitive data of other applications residing on the same chip. Currently, many efforts are made to secure smart card applets against one another using e.g. so called firewalls [6] [18] or byte code verification [13]. This is a cumbersome task. The cost of evaluating, for instance, an application written for MULTOS according to ITSEC E6 [7] is estimated to be 150% of the overall development cost [4]. Besides, their genericity does not allow to hard-wire once and for ever protection mechanisms needed to ensure the requirements of uniqueness and privacy described in the next section. Instead, each application has to implement its own security framework, possibly leading to new vulnerabilities.

# 3 Security Requirements

A multifunctional smart card as introduced in the first section should satisfy at least the following security requirements.

**Authenticity:** Only a legitimate issuer should be able to produce authentic virtual tokens for a given application. No one besides the student office should be capable of issuing valid student cards.

**Integrity:** A solution has to make sure that, once issued, a virtual token can not be modified, not even by its holder. The student must not be able to change the validity period of his card himself.

**Uniqueness:** Virtual tokens have to be protected against duplication. This is especially important when considering applications where the token is used as a dongle or as a ticket. Imagine a railway ticket that can be duplicated at will.

**Privacy:** This requirement could also be entitled "separability". Physical tokens, although perhaps belonging to the same user, are not a priori linked to each other. Often they are not even associated with their holder. In no way can a car key be linked to any of the other tokens a user has in his pocket, nor is it related to his person. The same should hold when replacing physical tokens by virtual ones. Else, profiles existing in the different systems could be easily matched to get a comprehensive picture of the user. Also, when virtual tokens need to be verified it should be possible to present them separated from each other, though residing on the same chip. All a train conductor has to know is that the traveller paid for his trip. This requires him to look at the passenger's ticket but not to learn his identity.

The requirements of authenticity and integrity are satisfied by letting the issuer digitally sign each virtual token he issues. Verifying this signature ensures that only authentic and untampered virtual tokens are accepted as valid. The scheme described in the next section also guarantees uniqueness and privacy.

# 4 New Approach

The proposed solution is based on the concept of virtual tokens (VT) introduced above. These are hosted by a microchip called *digital pocket* (DP) in this paper, in analogy to a pocket that holds physical tokens. VTs can be loaded (e.g. over the Internet) into a DP after the latter is issued (post-issuance loading). They can even be moved by their holder from one DP to another without any intervention by the issuer, which makes the scheme very flexible. In a certain way, VTs resemble attribute certificates as described e.g. in [3]. The main difference is that a VT can only be used in conjunction with a single hardware token (i.e. a DP) at a given time, thus preventing its duplication.

Each DP is embedded into a container that provides it with power supply and a communication interface. The most obvious realization of this idea is to use a smart card in conjunction with a reader providing the required infrastructure. However, it could be implemented as well in a mobile phone, in a wrist watch, or in any other object the user bears with him. For the sake of simplicity a smart card realization is assumed in this paper.

The main actors taking part in the scheme are identified in the next subsection. After sketching DP's architecture and describing the involved key pairs, the scheme is outlined in subsection 4.4. Finally, a short analysis of the trust relationships that have to be assumed among the different roles and a discussion comparing the new scheme to existing solutions are presented.

## 4.1 Roles

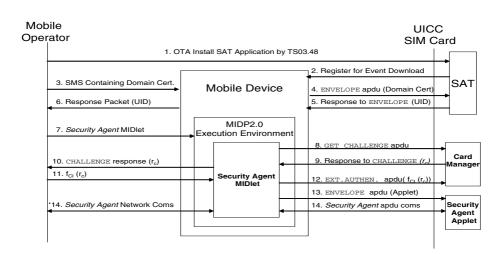

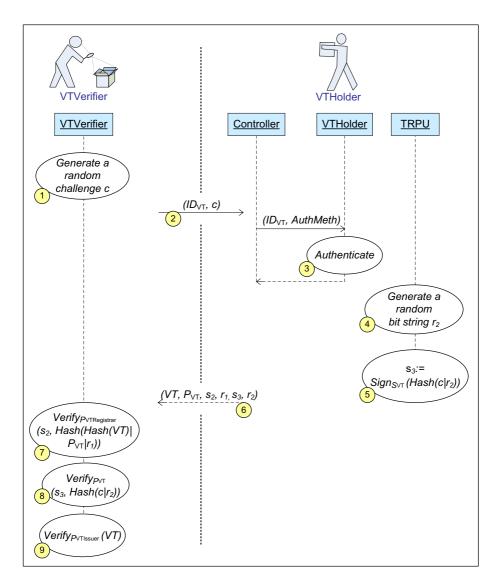

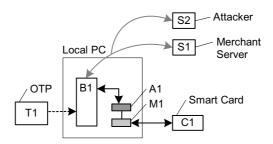

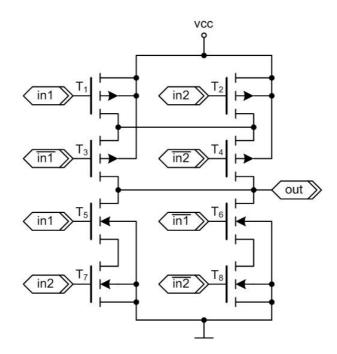

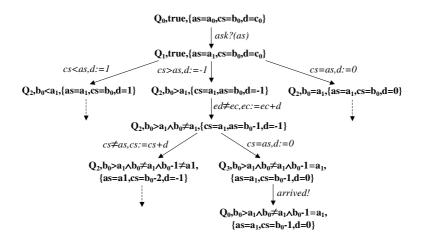

The following actors take part in the considered setting. Fig. 1 summarizes their interactions.

Fig. 1. The different roles and their interactions

- Digital Pocket Provider (DPProvider): is the issuer of DPs.

- Virtual Token Issuer (VTIssuer): issues VTs (e.g. the railway company).

- Virtual Token Holder (VTHolder): is a person holding one or more VTs (e.g. a railway passenger).

- Virtual Token Verifier (VTVerifier): verifies VTs (e.g. a train conductor).

- Virtual Token Registrar (VTRegistrar): represents a trusted institution assuring that there is no more than one active copy of a given VT at any time.

These roles may be assumed by distinct persons and/or institutions. However, a single organization may also assume several of them. DPProvider and VTRegistrar could for example be embodied by the same infrastructure operator. Another option is to have VTIssuer ensure the uniqueness of VTs he issues, thereby additionally playing VTRegistrar's role.

#### 4.2 Architecture

The proposed solution can be readily implemented using standard hardware components as they can be found on modern smart cards. More precisely, DP's architecture consists of the following elements.

- Protected Memory (PM): represents the area of the chip where VTs and all relevant public keys are stored. This area is accessible to VTHolder after

authorization, e.g. using a PIN or some kind of biometrics. The protection is meant to prevent VTVerifier or someone else from randomly reading the content of a DP without VTHolder's consent.<sup>1</sup>

- Tamper-Resistant Memory  $(TRM)^2$ : is an area that can not be read from the outside, not even by VTHolder. It serves as a storage for private keys.

- Tamper-Resistant Processing Unit (TRPU): represents a processing unit for the execution of computations involving secrets.

- Controller: coordinates the single actions of a DP and provides an interface to the outside world. It handles the communication with VTHolder, VTVerifier and VTRegistrar.

## 4.3 Involved Key Pairs

The presented solution relies on public key cryptography. In the remainder of this paper, a private key used to create a digital signature is always denoted by  $S_x$  (for some index x), whereas  $P_x$  stands for the corresponding public key employed for signature verification. More precisely, the following key pairs are used to generate and verify digital signatures in the different phases of the scheme.

- $(S_{\text{VTIssuer}}, P_{\text{VTIssuer}})$ : Every VT issued by a VTIssuer is signed with his private key  $S_{\text{VTIssuer}}$  and can be checked for validity using the corresponding public key  $P_{\text{VTIssuer}}$ .

- $(S_{\text{VTRegistrar}}, P_{\text{VTRegistrar}})$ : VTRegistrar employs his private key  $S_{\text{VTRegistrar}}$  to generate binding confirmations that can be verified using  $P_{\text{VTRegistrar}}$ .

- $(S_{\text{VT}}, P_{\text{VT}})$ : Each VT is bound to a DP using a dedicated key pair  $(S_{\text{VT}}, P_{\text{VT}})$ .  $(S_g, P_g)$ : Before their distribution, DPs are divided by DPProvider into groups.

All the DPs of a given group are assigned the same key pair  $(S_g, P_g)$ .

DPs are grouped in order to protect the privacy of their holders. That is, all DPs belonging to the same group g share a common key pair  $(S_g, P_g)$ . Thus, they cannot be distinguished from one another. If each DP had its own key pair, the different identities connected to it could be linked together. This is prevented by letting an individual DP hide in its group much in the same way that a single Internet user hides in a group of surfers when using anonymizer services built on crowds [15]. Although the fact that several chips carry the same private key would appear to increase the security risk, such is not the case. As will become clear from the following description of the scheme, the damage caused by a compromised DP is independent of whether it was assigned a unique key or whether it shares it with a number of other DPs.

<sup>&</sup>lt;sup>1</sup> To make such a protection effective a secure communication channel between VTHolder and DP is needed. This involves an input device (e.g. a keypad) and an output device (e.g. a small display) that are tamper-resistant. However, to keep the system's description simple this point will not be further elaborated in this paper.

<sup>&</sup>lt;sup>2</sup> As a perfect protection of hardware tokens averting every attack can hardly be achieved [1], the term "tamper-resistant" is used instead of "tamper-proof" to make clear that despite great efforts to protect the microchip, a risk of compromise still exists. The assumption is of course, as with other schemes, that the token's physical protection is sufficient for its purpose.

#### 4.4 How It Works

The main phases of the scheme comprise:

a) Initialization: Before its delivery to a VTHolder, each DP is initialized by DPProvider. To initialize a group of DPs, DPProvider generates a new key pair  $(S_g, P_g)$ . The private key  $S_g$  is stored in the tamper-resistant memory (TRM) of each card in the group. Further, the corresponding public key  $P_g$  is included into *PubList*, which is the list of the public keys of all DPs issued so far.<sup>3</sup>

**b)** Distribution: Once the DPs have been initialized, they can be distributed to VTHolders through any channel. At this stage, all the DPs are identical in the sense that they are neither VTHolder specific nor VTIssuer specific. A VTHolder could just buy an "empty" DP in the supermarket to load his VTs on it.

c) Virtual Token Generation: In order to issue a VT, VTIssuer has to write the application dependent data into a file and to sign it with his private key  $S_{\rm VTIssuer}$ . The format of this file may be freely chosen by VTIssuer (as long as VTVerifier is able to make sense of it). The signed file constituting a VT can be transferred to VTHolder via e-mail or any other means. If the VT contains confidential data it must, of course, be protected on its way to VTHolder. After receiving a VT, VTHolder has to bind it to a particular DP before it will be accepted by VTVerifier.

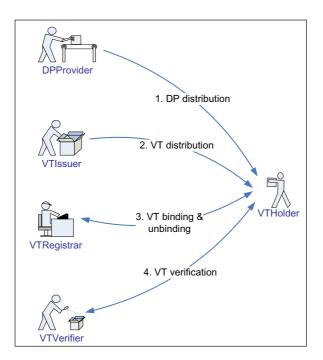

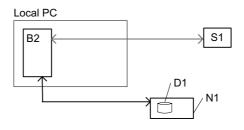

d) Binding: Binding a VT to a DP ensures that it can not be duplicated (see the requirement of uniqueness in section 3). VTRegistrar knows about every VT he has bound to a DP and is responsible for the prevention of multiple bindings. To do so, he stores the hash value of each VT that he binds in a list called *BoundList*. Storing only a hash value and not the VT itself prevents VTRegistrar from learning the token's content, thus guaranteeing VTHolder's privacy as required in section 3. Moreover, the use of a hash value improves the system's efficiency, especially when a big number of VTs has to be managed. The details of the binding process are depicted in protocol 1 (see also Fig. 2).

Protocol 1 (Binding of a VT to a DP by VTRegistrar):

1. TRPU calculates a hash value of VT:

$$h := Hash(VT).^4$$

- 2. A new key pair  $(S_{\rm VT}, P_{\rm VT})$  is generated inside TRPU.

- 3.  $S_{\rm VT}$  is stored in TRM.

$<sup>^3</sup>$  An update of PubList is regularly propagated to VTR egistrar (e.g. using a public key infrastructure).

<sup>&</sup>lt;sup>4</sup>  $Hash(\cdot)$  is assumed to be a cryptographically secure hash function, i.e. one that is collision and preimage resistant (see e.g. [11, p. 323]).

Fig. 2. Binding a VT to a DP by VTRegistrar (Protocol 1)

4. TRPU signs the bit string  $h|P_{\rm VT}$  using  $S_g$ :

$$s_1 := Sign_{S_q}(h|P_{\rm VT}).^5$$

- 5. The tuple  $(P_g, P_{VT}, h, s_1)$  is sent to VTRegistrar.

- 6. VTRegistrar verifies that  $P_g$  is contained in PubList.

- 7. VTRegistrar verifies that h is not yet contained in his list of bound VTs (BoundList).

- 8. VTRegistrar checks the validity of  $s_1$  using  $P_g$ :

$$Verify_{P_q}(s_1, h|P_{VT}).$$

- 9. VTRegistrar stores h in BoundList.

- 10. VTRegistrar generates a random bit string  $r_1$ .

- 11. VTRegistrar signs  $Hash(h|P_{VT}|r_1)$  with his private key  $S_{VTRegistrar}$ :

$s_2 := Sign_{S_{\rm VTRegistrar}}(Hash(h|P_{\rm VT}|r_1)).$

- 12. VTRegistrar sends the pair  $(s_2, r_1)$  back to VTHolder.

- 13. The tuple  $(ID_{\rm VT}, VT, P_{\rm VT}, s_2, r_1, AuthMeth)$  is stored in PM, where  $ID_{\rm VT}$  stands for the ID of the application VT belongs to and AuthMeth for the authentication method to enforce before granting access to this particular VT.<sup>6</sup>

By signing  $Hash(h|P_{VT}|r_1)$  in step 11 VTRegistrar confirms that the VT which hashes to h was bound to the DP that holds the corresponding private key  $S_{VT}$  in its TRM. Such a confirmation is only issued if three conditions are met:

- i. The binding was actually requested using a DP (step 8 of the previous protocol),

- ii. that DP is genuine, i.e. its public key  $P_g$  is contained in PubList (step 6), and

- iii. the VT in case is not yet bound to another DP (step 7).

Remark 1. If in step 11 VTRegistrar just signed  $h|P_{\rm VT}$  instead of  $Hash(h|P_{\rm VT}|r_1)$  then chosen-ciphertext attacks could be feasible. This is why [16, p. 54] points out that "it is foolish to encrypt arbitrary strings".

Remark 2. The key pair  $(S_{\rm VT}, P_{\rm VT})$  has to be generated securely inside the TRPU so that nobody learns its value. Some smart cards use pseudo random number generators with a seed set by the manufacturer [14]. Such smart cards are unsuitable for this scheme as everyone knowing the seed could deduct the entire pseudo random number sequence. The keys rather have to stem from a physical source of randomness (see e.g. [2] for a true random number generator suitable for integration on smart cards).

<sup>&</sup>lt;sup>5</sup>  $b_1|b_2$  stands for the concatenation of the bit strings  $b_1$  and  $b_2$ .