Tsutomu Sasao

# Memory-Based Logic Synthesis

# Memory-Based Logic Synthesis

## Tsutomu Sasao

# Memory-Based Logic Synthesis

Tsutomu Sasao Kyushu Institute of Technology Department of Computer Science and Electronic Iizuka, Japan sasao@cse.kyutech.ac.jp

ISBN 978-1-4419-8103-5 e-ISBN 978-1-4419-8104-2 DOI 10.1007/978-1-4419-8104-2 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011922264

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Preface**

This book describes the realization of logic functions using memories. The proposed methods can be used to impalement designs in field programmable gate arrays (FP-GAs) that contain both small-scale memories, called look-up tables (LUTs), and medium-scale memories, called embedded memories.

The basis for memory-based design is functional decomposition, which replaces a large memory with smaller ones. An LUT cascade is introduced as a new architecture for logic synthesis. This book introduces the C-measure, which specifies the complexity of Boolean functions. Functions with a suitably small C-measure can be efficiently realized by LUT cascades.

This book also shows logic design methods for index generation functions. An index generation function is a mathematical model for an address table which can be used to store internet addresses. Such a table must be updated frequently, and the operation must be performed as fast as possible. In addition, this book introduces hash-based design methods, which efficiently realize index generation functions by pairs of smaller memories. Main applications include: IP address table lookup, packet filtering, terminal access controllers, memory patch circuits, virus scan circuits, fault map of memory, and pattern matching.

This book is suitable for both FPGA system designers and CAD tool developers. To read the book, a basic knowledge of logic design and discrete mathematics is required. Each chapter contains examples and exercises. Solutions for the exercises are also provided.

Tsutomu Sasao

## Acknowledgements

This research is supported in part by the Grants in Aid for Scientific Research of JSPS, the grants of MEXT knowledge Cluster Project, and Regional Innovation Cluster Program. Many people were involved in this project: Jon T. Butler, Masayuki Chiba, Bogdan Falkowski, Yukihiro Iguchi, Kazunari Inoue, Atsumu Iseno, Yoshifumi Kawamura, Hisashi Kajihara, Munehiro Matsuura, Alan Mishchenko, Hiroki Nakahara, Kazuyuki Nakamura, Shinobu Nagayama, Marek Perkowski, Hui Qin, Marc Riedel, Takahiro Suzuki, Akira Usui, and Yuji Yano.

Most materials in this book have been presented at various conferences: IWLS, DSD, ISMVL, ICCAD, ICCD, DAC, ASPDAC, FPL, ARC, and SASIMI, as well as journals: IEEETCAD, IEICE and IJE. In many cases, reviewers comments considerably improved the quality of the materials.

Preliminary versions of this book were used as a textbook for seminars in our group. Numerous improvements were proposed by the students of Kyushu Institute of Technology: Taisuke Fukuyama, Takuya Nakashima, Takamichi Torikura, Satoshi Yamaguchi, Takuya Eguchi, Yoji Tanaka, Yosuke Higuchi, Takahiro Yoshida, and Meiji University: Atsushi Ishida, Kensuke Kitami, Koki Shirakawa, Kengo Chihara, Shotaro Hara, Akira Yoda.

Prof. Jon T. Butler read through the entire manuscript repeatedly and made important corrections and improvements.

Dr. Alan Mishchenko's comments on the final manuscript were also appreciated.

# **Contents**

| 1 | Intro | oduction                                            | 1  |

|---|-------|-----------------------------------------------------|----|

|   | 1.1   | Motivation                                          | 1  |

|   | 1.2   | Organization of the Book                            | 1  |

| 2 | Basi  | c Elements                                          | 3  |

|   | 2.1   | Memory                                              | 3  |

|   | 2.2   | Programmable Logic Array                            | 4  |

|   | 2.3   | Content Addressable Memory                          | 4  |

|   | 2.4   | Field Programmable Gate Array                       | 6  |

|   | 2.5   | Remarks                                             | 8  |

|   | Prob  | lems                                                | 8  |

| 3 | Defi  | nitions and Basic Properties                        | 11 |

|   | 3.1   | Functions                                           | 11 |

|   | 3.2   | Logical Expression                                  | 11 |

|   | 3.3   | Functional Decomposition                            | 12 |

|   | 3.4   | Binary Decision Diagram                             | 14 |

|   | 3.5   | Symmetric Functions                                 |    |

|   | 3.6   | Technology Mapping                                  | 21 |

|   | 3.7   | The Mathematical Constant <i>e</i> and Its Property | 23 |

|   | 3.8   | Remarks                                             |    |

|   | Prob  | lems                                                | 24 |

| 4 | MU    | X-Based Synthesis                                   | 25 |

|   | 4.1   | Fundamentals of MUX                                 |    |

|   | 4.2   | MUX-Based Realization                               |    |

|   | 4.3   | Remarks                                             |    |

|   | Drob  | lame                                                | 32 |

x Contents

| 5 | Casc  | ade-Based Synthesis                               | . 33 |

|---|-------|---------------------------------------------------|------|

|   | 5.1   | Functional Decomposition and LUT Cascade          |      |

|   | 5.2   | Number of LUTs to Realize General Functions       | . 35 |

|   | 5.3   | Number of LUTs to Realize Symmetric Functions     | . 38 |

|   | 5.4   | Remarks                                           |      |

|   | Probl | lems                                              |      |

| 6 | Enco  | oding Method                                      |      |

|   | 6.1   | Decomposition and Equivalence Class               |      |

|   | 6.2   | Disjoint Encoding                                 |      |

|   | 6.3   | Nondisjoint Encoding                              |      |

|   | 6.4   | Remarks                                           | . 53 |

|   | Probl | lems                                              | . 53 |

| 7 | Func  | etions with Small C-Measures                      | . 55 |

|   | 7.1   | C-Measure and BDDs                                | . 55 |

|   | 7.2   | Symmetric Functions                               | . 56 |

|   | 7.3   | Sparse Functions                                  | . 57 |

|   | 7.4   | LPM Functions                                     | . 57 |

|   | 7.5   | Segment Index Encoder Function                    | 60   |

|   | 7.6   | WS Functions                                      | 62   |

|   | 7.7   | Modulo Function                                   | 65   |

|   | 7.8   | Remarks                                           | 67   |

|   | Probl | lems                                              | 67   |

| 8 | C-M   | easure of Sparse Functions                        | . 71 |

|   | 8.1   | Logic Functions with Specified Weights            | . 71 |

|   | 8.2   | Uniformly Distributed Functions                   | . 76 |

|   | 8.3   | Experimental Results                              | . 77 |

|   |       | 8.3.1 Benchmark Functions                         | . 77 |

|   |       | 8.3.2 Randomly Generated Functions                | . 78 |

|   | 8.4   | Remarks                                           |      |

|   | Probl | lems                                              | . 80 |

| 9 | Inde  | x Generation Functions                            | . 81 |

|   | 9.1   | Index Generation Functions and Their Realizations | 81   |

|   | 9.2   | Address Table                                     | . 81 |

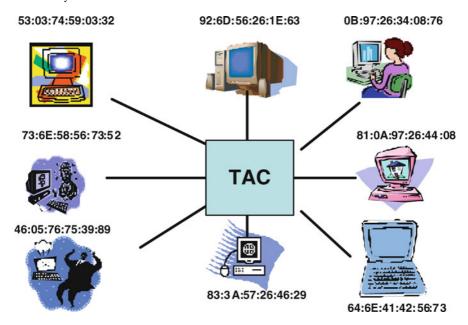

|   | 9.3   | Terminal Access Controller                        |      |

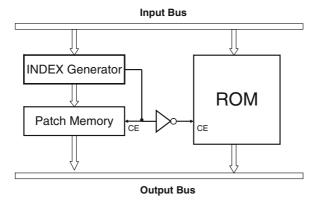

|   | 9.4   | Memory Patch Circuit                              |      |

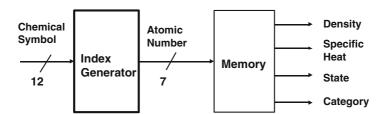

|   | 9.5   | Periodic Table of the Chemical Elements           |      |

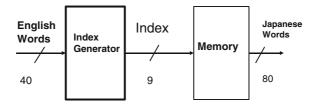

|   | 9.6   | English–Japanese Dictionary                       |      |

|   | 9.7   | Properties of Index Generation Functions          | 86   |

|   | 9.8   | Realization Using $(p,q)$ -Elements               |      |

|   | 9.9   | Realization of Logic Functions with Weight $k$    |      |

|   | 9.10  | Remarks                                           |      |

|   |       | lems                                              | 93   |

Contents xi

| 10 | Hash  | -Based S  | Synthesis                                    | 95   |

|----|-------|-----------|----------------------------------------------|------|

|    | 10.1  |           | unction                                      |      |

|    | 10.2  | Index C   | Generation Unit                              | 96   |

|    | 10.3  | Reduct    | ion by a Linear Transformation               | 100  |

|    | 10.4  | Hybrid    | Method                                       | 103  |

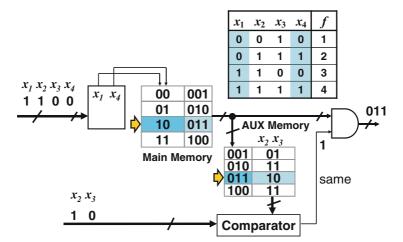

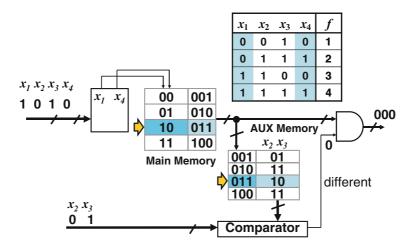

|    | 10.5  | Registe   | ered Vectors Realized by Main Memory         | 106  |

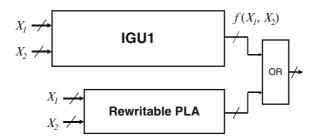

|    | 10.6  | Super I   | Hybrid Method                                | 108  |

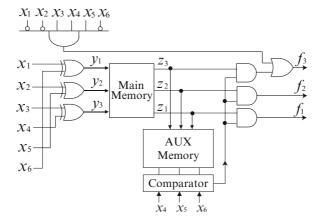

|    | 10.7  | Parallel  | Sieve Method                                 | 111  |

|    | 10.8  | Experi    | mental Results                               |      |

|    |       | 10.8.1    | List of English Words                        |      |

|    |       | 10.8.2    | Randomly Generated Functions                 |      |

|    |       | 10.8.3    | IP Address Table                             | 115  |

|    | 10.9  |           | KS                                           |      |

|    | Probl | ems       |                                              | 116  |

|    |       |           |                                              |      |

| 11 |       |           | the Number of Variables                      |      |

|    | 11.1  |           | zation for Incompletely Specified Functions  |      |

|    | 11.2  |           | ions and Basic Properties                    |      |

|    | 11.3  |           | hm to Minimize the Number of Variables       |      |

|    | 11.4  |           | is for Single-Output Logic Functions         |      |

|    | 11.5  |           | ion to Multiple-Output Functions             | 126  |

|    |       | 11.5.1    | Number of Variables to Represent Index       | 4.05 |

|    |       |           | Generation Functions                         | 127  |

|    |       | 11.5.2    | Number of Variables to Represent General     | 4.00 |

|    | 11.6  |           | Multiple-Output Functions                    |      |

|    | 11.6  | _         | mental Results                               |      |

|    |       | 11.6.1    | Random Single-Output Functions               |      |

|    |       | 11.6.2    | Random Index Generation Functions            |      |

|    |       | 11.6.3    | IP Address Table                             |      |

|    | 11.7  | 11.6.4    | Benchmark Multiple-Output Functions          |      |

|    | 11.7  |           | ks                                           |      |

|    | Probl | ems       |                                              | 133  |

| 12 | Vario | nıc Reali | izations                                     | 137  |

| 1- | 12.1  |           | ation Using Registers, Gates, and An Encoder |      |

|    | 12.2  |           | ascade Emulator                              |      |

|    | 12.3  |           | ation Using Cascade and AUX Memory           |      |

|    | 12.4  |           | rison of Various Methods                     |      |

|    | 12.5  |           | Converter                                    |      |

|    | 12.6  |           | KS                                           |      |

|    |       |           |                                              |      |

|    | 11001 |           |                                              |      |

| 13 | Conc  | lusions   |                                              | 151  |

| xii | Contents |

|-----|----------|

|     |          |

| Solutions    | 153 |

|--------------|-----|

| Bibliography | 179 |

| Index        | 187 |

# Chapter 1 Introduction

#### 1.1 Motivation

Two of the most crucial problems in VLSI design are their high design cost and long design time. A solution to these problems is to use programmable architectures. Programmable LSIs reduce the hardware development cost and time drastically, since one LSI can be used for various applications. This book considers realizations of logic functions by programmable architectures. Various methods exist to realize multiple-output logic functions by programmable architectures. Among them, memories and programmable logic arrays (PLAs) directly realize logic functions. However, when the number of input variables n is large, the necessary hardware becomes too large. Thus, field programmable gate arrays (FPGAs) are widely used. Unfortunately, FPGAs require layout and routing in addition to logic design. Thus, quick reconfiguration is not so easy.

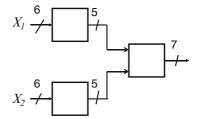

A look-up table (LUT) cascade is a series connection of memories. It efficiently realizes various classes of logic functions. Since the architecture is simple, LUT cascades are suitable for the applications where frequent update is necessary. This book explores the design and application of LUT cascades. In addition, it shows memory-based methods to realize index generation functions, which are useful for pattern matching and communication circuits.

## 1.2 Organization of the Book

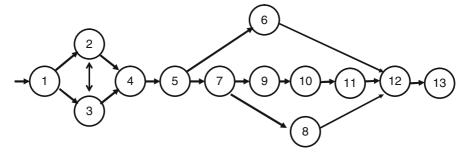

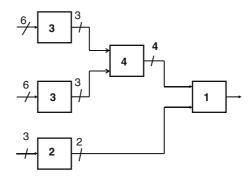

This book consists of 13 chapters. Figure 1.1 shows the relation between the chapters, where the arrows show the order to read the chapters. For example, Chaps. 6 and 7 can be read after reading Chap. 5. Chapter 2 reviews the basic elements used in this book: memory, PLA, content addressable memory (CAM), and FPGA.

Chapter 3 reviews the definitions and basic properties of logic functions. Functional decomposition is the most important theory covered.

2 1 Introduction

Fig. 1.1 Relation among chapters

Chapter 4 shows multiplexer-based synthesis of logic functions. This method is universal, i.e., it can realize any logic function. However, the number of LUTs required to realize the function tends to increase exponentially with n, the number of input variables.

Chapter 5 shows a method to realize logic functions using LUT cascades. This method is not universal, i.e., it can be applied to only a limited class of logic functions. However, the number of LUTs to realize the function tends to increase linearly with n, the number of input variables. The C-measure is used to estimate the circuit size.

Chapter 6 shows a method to reduce the number of LUTs by considering the encoding of the functional decomposition.

Chapter 7 shows a class of functions whose C-measures are small. Such functions are efficiently realized by LUT cascades.

Chapter 8 considers the C-measure of the functions whose number of minterms is limited. It shows that when the number of minterms is small, the C-measure is also small.

Chapter 9 introduces index generation functions, which are useful to design IP address tables, terminal access controllers for local area network, etc.

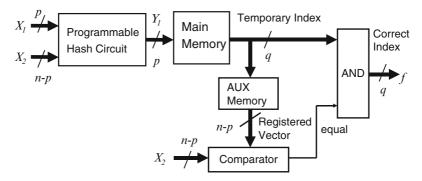

Chapter 10 introduces a hash-based synthesis of index generation functions. The method is similar to a hash table for software. Similar to the case of software realization, collisions of data may occur. However, in hardware, we can avoid collisions by using various circuits that work concurrently.

Chapter 11 shows a reduction method for the number of variables for the hash circuit. It introduces incompletely specified functions and shows an algorithm to reduce the number of variables.

Chapter 12 shows various methods to realize index generation functions.

Chapter 13 summarizes the book.

# Chapter 2 Basic Elements

This chapter reviews memory, programmable logic array (PLA), content addressable memory (CAM), and field programmable gate array (FPGA).

#### 2.1 Memory

Semiconductor memories have a long history of research, and various types of memories have been developed.

A dynamic random access memory (**DRAM**) uses only a single transistor to store one bit. However, the peripheral circuit is rather complex, and periodical refreshing is necessary. Thus, DRAM is suitable for large-scale memory, but not for a small-scale memory.

A static random access memory (**SRAM**) uses six transistors to store one bit. The peripheral circuit is not so complex as in DRAM, and refreshing is unnecessary. Thus, SRAM is suitable for small-scale memory, but not for large-scale memory. Both DRAM and SRAM are **volatile**, i.e., if the power supply is tuned off, the data are lost.

Read only memories (**ROM**s), however are **nonvolatile** and are used for storing fixed data. For rewritable ROMs, fabrication often requires a dedicated process and such ROMs are expensive.

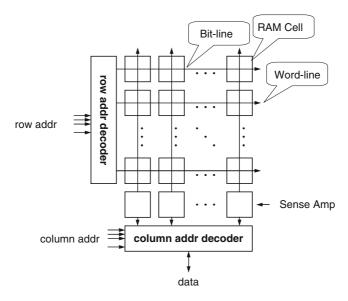

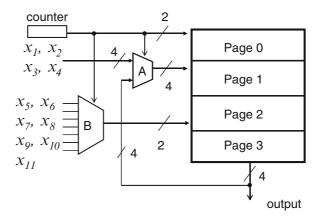

To reduce the amount of hardware, memories are often implemented as a twodimensional structure that is shown in Fig. 2.1. The row address decoder selects one row. And the sense amplifiers read the data for the selected row. Finally, the column address decoder selects one bit from the word. In many cases, the memory has a clock. Such a memory is **synchronous**. Many FPGAs contain memories, and many of them are synchronous. However, **asynchronous** memories (i.e., memories operating without clock pulses) are also available. 4 2 Basic Elements

Fig. 2.1 Memory architecture

#### 2.2 Programmable Logic Array

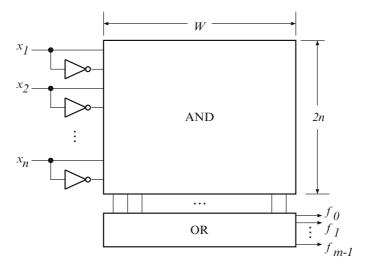

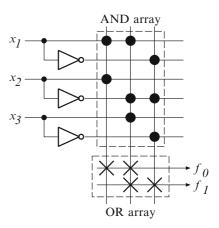

**PLAs** were often used for implementing controllers of microprocessors [94]. A PLA consists of the AND array and the OR array as shown in Fig. 2.2. For example, a 3-input 2-output function can be implemented as shown in Fig. 2.3. In the AND array, a cross-point denotes the AND connection, while in the OR array, a cross-point denotes the OR connection. Both **static** and **dynamic PLAs** exist. In the dynamic PLA, a clock pulse is used to read out the data. For large-scale PLAs, dynamic realizations are often used, since static CMOS realization is too large and the NMOS realization dissipates much static power. In a **rewritable PLA**, each cross-point consists of a switch and a memory element [3]. Let n be the number of inputs, W be the number of columns, and m be the number of outputs. Then, the size of a PLA is approximated by W(2n + m). The number of columns W can be reduced by minimizing sum-of-products (SOPs) expressions. Thus, the logic design is relatively easy.

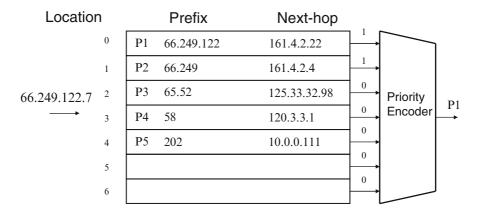

#### 2.3 Content Addressable Memory

An ordinary memory such as that introduced in Sect. 2.1 uses a memory address to access data and return the contents of the memory. On the contrary, a **CAM** searches using the contents of the memory, and returns the address where the supplied data were found.

Fig. 2.2 Programmable logic array (PLA)

Fig. 2.3 An example of PLA

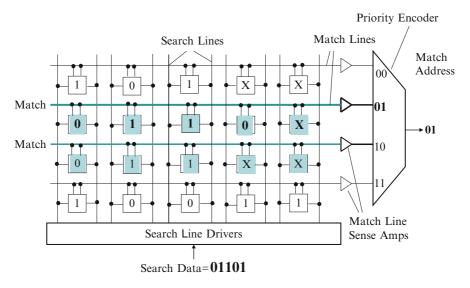

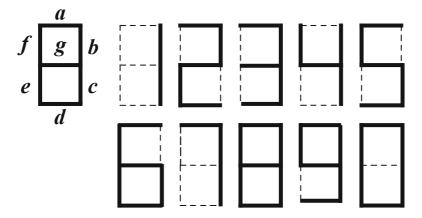

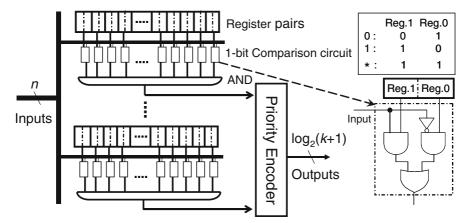

CAMs are often used in pattern matching [5]. Two types of CAMs exist: a binary CAM (**BCAM**) and a ternary CAM (**TCAM**). In a BCAM, each cell can take one of two states: 0 and 1. BCAMs are used for exact match. In a TCAM, each cell can take one of three states: 0, 1, and X (*don't care* that matches both 0 and 1). A TCAM can be used for implementing the longest prefix match to be explained in Chap. 7, and range match. To store one bit of information, an SRAM requires 6 transistors, while a TCAM requires 16 transistors [90]. Thus, a TCAM is more expensive than SRAM. Figure 2.4 shows an example of a CAM. In the CAM, for the input (i.e., search data) 01101, the second and the third rows match. However, the **priority encoder** selects the lowest address, i.e., 01. Thus, the output of the CAM is 01, the address of the second line. When the input is 11111, the CAM shows that there is no match.

6 2 Basic Elements

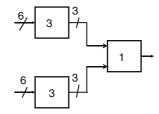

Fig. 2.4 CAM architecture

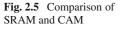

Figure 2.5 compares an SRAM with a CAM. Note that in an SRAM, only one row is activated at a time, while in a CAM, all the rows are activated at the same time. In a CAM, all the rows are charged and discharged in every search operation. Thus, a CAM dissipates more power than an SRAM with the same number of bits.

# 2.4 Field Programmable Gate Array

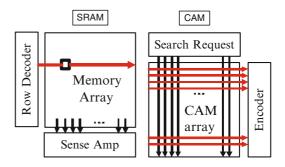

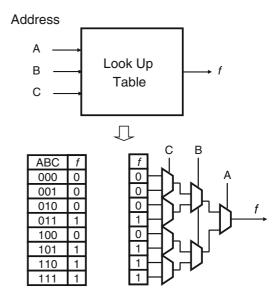

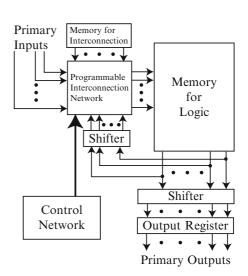

Most **FPGA**s have an **island-style** architecture as shown in Fig. 2.6. In this architecture, logic elements are surrounded by interconnection elements such as switch blocks, connection blocks, and wiring. Logic elements are, in most cases, look-up tables (**LUT**s). A *K*-**LUT** is a module that realizes an arbitrary *K*-variable function. Thus, logically it is a *K*-input memory. However, unlike an ordinary

Fig. 2.6 Island-style FPGA

Fig. 2.7 LUT for FPGA

(large-scale) memory presented before, it is often implemented by a register and selector as shown Fig. 2.7. No clock pulse is necessary to read out the data; therefore, it is asynchronous. In modern FPGAs, more than 90% of the chip area is for interconnections. Thus, layout design is as important as logic design. Also, layout design often requires more CPU time than logic design.

Most FPGAs use SRAMs to store configuration data. At power-up, FPGAs are blank, and an external nonvolatile memory (EEPROM, flash RAM, MRAM, or FeRAM) is used to restore the configuration data into SRAM. FPGAs need to be configured from the external nonvolatile memory at every system power-up time. The configuration time is tens to hundreds of milliseconds. Also, the

8 2 Basic Elements

SRAM for configuration must be kept on even when the system is not used. As programmable circuits become larger, the numbers of LUTs and embedded memories increase, and the power dissipation of SRAMs due to leakage current becomes more serious. In the past, FPGAs with 4 or 5 input LUTs were believed to be the most efficient [99, 100]; however, in the current technology, FPGAs with 6 inputs are the standard [4, 7, 158]. Thus, we have the following:

*Problem*: Given an *n*-variable (multiple-output) function f, find the minimum number of 6-LUTs needed to realize f, where  $n \le 20$ .

Unfortunately, this is a very hard problem. So, we try to obtain an upper bound by using properties or measures of the function. A property of the function should be easy to detect, such as symmetry, and measures should be efficient to calculate. Such measures include:

- The number of variables (i.e., the support size)

- The weight of the function [133]

- The C-measure of a function [133]

- The number of products in the SOP [78]

- The number of literals in the factored expression [78]

- The number of nodes in the decision diagram [107]

Chapters 4 and 5 consider the number of *K*-LUTs to realize a given function.

#### 2.5 Remarks

This chapter briefly introduced memory, CAM, and FPGA. As for FPGAs, various architectures are shown in Refs. [15, 100]. As for logic synthesis of FPGAs, see Refs. [20, 78]. In recent FPGAs, the architecture is quite complicated, and a single FPGA can implement a multiprocessor system.

Many commercial FPGAs contain memories in addition to LUTs. They are called **embedded memories** [4] or **embedded block RAMs** [156].

#### **Problems**

- **2.1.** Design the CAM function shown in Fig. 2.4 by using a PLA.

- **2.2.** Explain why asynchronous memories are used for LUTs in FPGAs instead of synchronous ones.

- **2.3.** In the past, 4-LUTs or 5-LUTs were mainly used in FPGAs. However, nowadays, 6-LUTs are popular in FPGAs. Discuss the reason why 6-LUTs are preferred.

- **2.4.** Explain why dynamic CMOS is used instead of static CMOS in PLAs.

2.5 Remarks 9

**2.5.** Suppose that a TCAM with n inputs and W words is given. Show a method to implement the same function as the TCAM by using a PLA.

**2.6.** Suppose that a PLA with n inputs, m outputs, and W products is given. Show a method to implement the same function as the PLA by using a TCAM and a memory.

#### Chapter 3

## **Definitions and Basic Properties**

This chapter first introduces logical expressions and functional decomposition. Then, it introduces some properties of symmetric functions.

#### 3.1 Functions

**Definition 3.1.1.** A mapping  $F: B^n \to \{0, 1, \dots, k-1\}$ , where  $B = \{0, 1\}$  is a **binary-input integer valued function**. A mapping  $F: B^n \to B$ , where  $B = \{0, 1\}$  is a **logic function**. If  $F(\vec{a}_i) \neq 0$   $(i = 1, 2, \dots, k)$  for k different input vectors, and F = 0 for other  $(2^n - k)$  input vectors, then the **weight** of the function is k.

#### 3.2 Logical Expression

**Definition 3.2.1.** Binary variables are represented by  $x_i$  (i = 1, 2, ..., n). A **literal** of a variable  $x_i$  is either  $x_i$ ,  $\bar{x}_i$ , or the constant 1. An AND of literals is a **product**, and an OR of products is a **sum-of-products** (**SOP**) **expression**.

**Definition 3.2.2.** Let  $B = \{0, 1\}$ ,  $X = (x_1, x_2, \dots, x_t)$ , and  $x_i$  can take a value in B. Then, we can consider that X takes its value from  $P = \{0, 1, \dots, 2^t - 1\}$ . Let S be a subset  $(S \subseteq P)$  of P. Then,  $X^S$  is a **literal** of X. When  $X \in S$ ,  $X^S = 1$ , and when  $X \notin S$ ,  $X^S = 0$ . Let  $S_i \subseteq P_i$   $(i = 1, 2, \dots, n)$ , then  $X_1^{S_1} X_2^{S_2} \cdots X_n^{S_n}$  is a **logical product**.  $\bigvee_{(S_1, S_2, \dots, S_n)} X_1^{S_1} X_2^{S_2} \cdots X_n^{S_n}$  is a **SOP** expression. If  $S_i = P_i$ , then  $X_i^{S_i} = 1$  and the logical product is independent of  $X_i$ . In this case, the literal  $X_i^{S_i}$  is redundant and can be omitted. A logical product is also called a **term** or a **product term**.

*Example 3.2.1.* When t = 2, we have  $P = \{0, 1, 2, 3\}$ , and  $X = (x_1, x_2)$  takes four values. In this case,  $X^{\{1\}}$ ,  $X^{\{1,2\}}$ , and  $X^{\{0,1,2,3\}}$  are literals. Suppose that  $P_1 = P_2 = P_3 = \{0, 1, 2, 3\}$ . Then,

$$F = X_{1}^{\{0,1,2,3\}} X_{2}^{\{0\}} X_{3}^{\{0\}} \vee X_{1}^{\{0,1\}} X_{2}^{\{0,1,2,3\}} X_{3}^{\{1,3\}} \\ \vee X_{1}^{\{0,1\}} X_{2}^{\{2\}} X_{3}^{\{0,1,2,3\}}$$

is a SOP. Note that  $X^{\{0,1,2,3\}} = 1$ . In this case,  $X^{\{0,1,2,3\}}$  is redundant and can be omitted. By removing redundant literals, this expression can be simplified to

$$F = X_2^{\{0\}} X_3^{\{0\}} \vee X_1^{\{0,1\}} X_3^{\{1,3\}} \vee X_1^{\{0,1\}} X_2^{\{2\}}.$$

#### 3.3 Functional Decomposition

**Definition 3.3.1.** [8] Let f(X) be a logic function, and  $(X_1, X_2)$  be a partition of the input variables, where  $X_1 = (x_1, x_2, \ldots, x_k)$  and  $X_2 = (x_{k+1}, x_{k+2}, \ldots, x_n)$ . The **decomposition chart** for f is a two-dimensional matrix with  $2^k$  columns and  $2^{n-k}$  rows, where each column and row is labeled by a unique binary code, and each element corresponds to the truth value of f. The function represented by a column is a **column function** and is dependent on  $X_2$ . Variables in  $X_1$  are **bound variables**, while variables in  $X_2$  are **free variables**. In the decomposition chart, the **column multiplicity** denoted by  $\mu_k$  is the number of different column patterns.

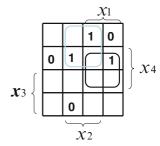

Example 3.3.1. Figure 3.1 shows a decomposition chart of a 4-variable function.  $\{x_1, x_2\}$  are the bound variables, and  $\{x_3, x_4\}$  are the free variables. Since all the column patterns are different and there are four of them, the column multiplicity is  $\mu_2 = 4$ .

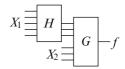

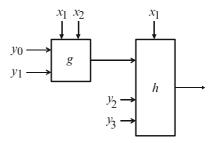

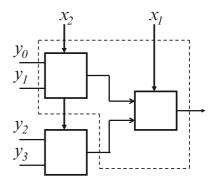

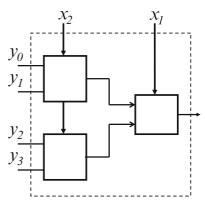

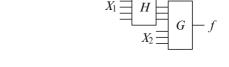

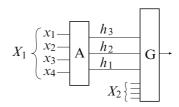

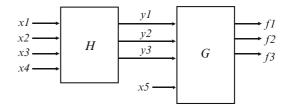

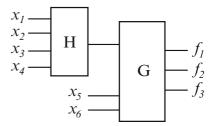

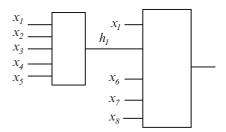

**Theorem 3.3.1.** [25] For a given function f, let  $X_1$  be the bound variables, let  $X_2$  be the free variables, and let  $\mu_k$  be the column multiplicity of the decomposition chart. Then, the function f can be realized with the network shown in Fig. 3.2. In this case, the number of signal lines connecting blocks H and G is  $\lceil \log_2 \mu_k \rceil$ .

When the number of signal lines connecting two blocks is smaller than the number of input variables in  $X_1$ , we can often reduce the total amount of memory by the realization in Fig. 3.2 [51]. When  $\mu_k = 2$ , it is an **Ashenhurst decomposition** [8] or

**Fig. 3.1** Decomposition chart of a logic function

**Fig. 3.2** Realization of a logic function by decomposition

a simple disjoint decomposition. When  $\mu_k > 2$ , it is a Curtis decomposition [25], also called **Roth–Karp decomposition** [101] or a **generalized decomposition**. The number of functions with Curtis decompositions is much larger than those with Ashenhurst decompositions.

A function with an Ashenhurst decomposition can be written as

$$f(X_1, X_2) = g(h_1(X_1), X_2).$$

A function with a Curtis decomposition can be written as

$$f(X_1, X_2) = g(h_1(X_1), h_2(X_1), \dots, h_m(X_1), X_2),$$

where  $m = \lceil \log_2 \mu \rceil$ .

**Lemma 3.3.1.** Consider a decomposition chart for  $f(X_1, X_2)$ , where  $X_1 = (x_1, x_2, ..., x_k)$  and  $X_2 = (x_{k+1}, x_{k+2}, ..., x_n)$ . Then, the column multiplicity does not change under the permutation of variables within  $X_1$  and  $X_2$ . Thus,

$$\mu(f(X_1, X_2)) = \mu(f(\tilde{X_1}, \tilde{X_2})),$$

where  $\tilde{X}_1 = (x_{\pi(1)}, x_{\pi(2)}, \dots, x_{\pi(k)}), \ \tilde{X}_2 = (x_{\lambda(k+1)}, x_{\lambda(k+2)}, \dots, x_{\lambda(n)}), \ and, \ \pi$  and  $\lambda$  denote the permutation on  $\{1, 2, \dots, k\}$  and  $\{k+1, k+2, \dots, n\}$ , respectively.

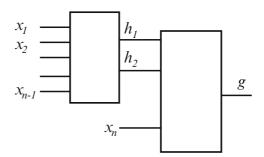

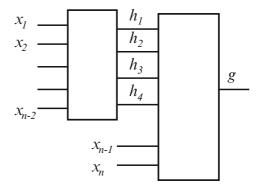

**Lemma 3.3.2.** An arbitrary function of n variables can be decomposed as

- 1.  $f(X_1, X_2) = g(h_1(X_1), h_2(X_1), X_2)$ , where  $X_1 = (x_1, x_2, \dots, x_{n-1})$  and  $X_2 = (x_n)$ .

- 2.  $f(X_1, X_2) = g(h_1(X_1), h_2(X_1), h_3(X_1), h_4(X_1), X_2))$ , where  $X_1 = (x_1, x_2, ..., x_{n-2})$  and  $X_2 = (x_{n-1}, x_n)$ .

Figures 3.3 and 3.4 show the circuits for the above decompositions.

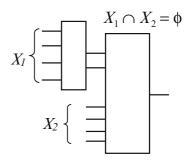

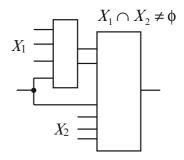

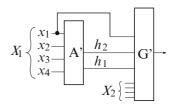

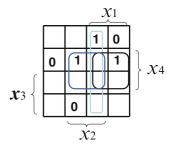

A functional decomposition can be of two types: A **disjoint decomposition**, where the bound set and the free set are disjoint, as shown in Fig. 3.5. A **nondisjoint decomposition**, where the bound set and free set have at least one common element. Figure 3.6 shows the case where one variable is shared by the bound set and the free set.

**Fig. 3.3** Decomposition of an arbitrary function, where  $X_2 = (x_n)$

Fig. 3.5 Disjoint decomposition

**Fig. 3.6** Nondisjoint decomposition

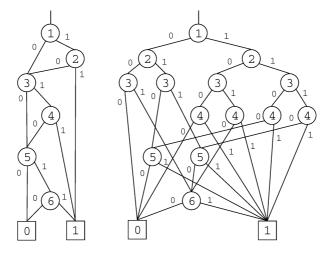

### 3.4 Binary Decision Diagram

A binary decision diagram (BDD) [12] is a graphical representation of a logic function. It often has a more compact representation than other methods. Thus, BDDs are widely used in the computer-aided design of logic networks [65].

**Definition 3.4.1.** A BDD is a directed acyclic graph (DAG) with two terminal nodes: the 0-terminal node and the 1-terminal node. Each nonterminal node is labeled by an index of an input variable of the Boolean function, and has two outgoing edges: the 0-edge and the 1-edge. An **ordered BDD** (**OBDD**) is a BDD such that the input variables appear in a fixed order in all the paths of the graph, and each variable appears at most once in a path.

Fig. 3.7 Node elimination

Fig. 3.8 Node sharing

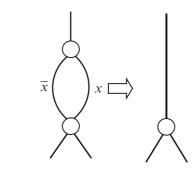

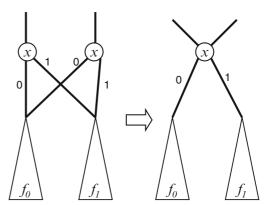

**Definition 3.4.2.** A **reduced ordered BDD** (**ROBDD**) is obtained from an OBDD by applying the following two reduction rules:

- 1. Eliminate all the redundant nodes whose two edges point to the same node (Fig. 3.7).

- 2. Share all the equivalent nodes (Fig. 3.8).

A **quasi-reduced ordered BDD** (**QROBDD**) is obtained from an OBDD by applying the second reduction rule only.

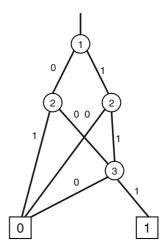

Example 3.4.1. Figure 3.9 is a ROBDD for

$$f(x_1, x_2, x_3) = (\bar{x}_1 \bar{x}_2 \vee x_1 x_2) x_3.$$

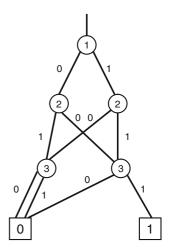

On the other hand, Fig. 3.10 is a QROBDD for the same function. In Fig. 3.10, the left node for  $x_3$  is redundant, and eliminated in the ROBDD. Note that in an QROBDD, all the paths from the root node to a terminal node encounter all the variables.

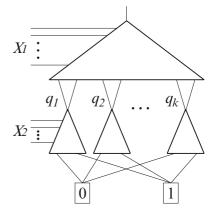

**Theorem 3.4.1.** Let  $X = (X_1, X_2)$  be a partition of X. Suppose that the QROBDD for f(X) is partitioned into two blocks as shown in Fig. 3.11. Let k be the number of

Fig. 3.9 Reduced ordered BDD

Fig. 3.10 Quasi-reduced OBDD

**Fig. 3.11** Computation of column multiplicity for functional decomposition  $f(X_1, X_2) = g(h(X_1), X_2)$

the nodes in the lower block that is adjacent to the upper block, and  $\mu$  be the column multiplicity of the decomposition chart for  $f = g(h(X_1), X_2)$ . Then,  $k = \mu$ .

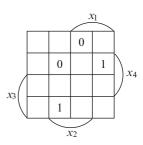

Example 3.4.2. Consider the function represented by the BDD in Figs. 3.9 and 3.10. Let  $X_1 = (x_1, x_2)$  and  $X_2 = (x_3)$ . Then, the number of the nodes in the lower block that are adjacent to the upper block is two. The function can be decomposed as  $f(X_1, X_2) = g(h(X_1), X_2)$ , where  $h(X_1) = \bar{x}_1 \bar{x}_2 \vee x_1 x_2$ , and  $g(h, X_2) = h x_3$ . Figure 3.12 shows the decomposition chart. Note that the column multiplicity is two. In Fig. 3.10, the left node for  $x_3$  represents the constant 0 function, while the right node for  $x_3$  represents the  $x_3$  function. It is clear that the number of different column patterns in the decomposition chart is equal to the number of nodes for  $x_3$  in the QROBDD [106].

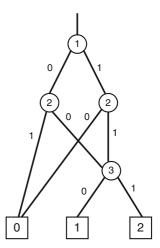

**Definition 3.4.3.** A **multiterminal BDD** (**MTBDD**) is an extension of a BDD with multiple terminal nodes, each of which has an integer value.

An MTBDD can be used to represent a multiple-output function.

Example 3.4.3. Figure 3.13 is an MTBDD for 3-valued output function. Note that it is a reduced ordered MTBDD (ROMTBDD), but is not a quasi-reduced ordered MTBDD (QROMTBDD).

**Fig. 3.12** Decomposition table of a logic function

**Fig. 3.13** Multiterminal BDD

#### 3.5 Symmetric Functions

Functions that appear in arithmetic circuits, such as adders, often have symmetries. When logic functions have certain symmetries, they are often realized using fewer elements.

**Definition 3.5.1.** A function f is **totally symmetric** if any permutation of the variables in f does not change the function. A totally symmetric function is also called a **symmetric function**.

**Definition 3.5.2.** In a function  $f(x_1, \ldots, x_i, \ldots, x_j, \ldots, x_n)$ , if the function  $f(x_1, \ldots, x_j, \ldots, x_i, \ldots, x_n)$  that is obtained by interchanging variables  $x_i$  with  $x_j$  is equal to the original function, then f is **symmetric with respect to**  $x_i$  **and**  $x_j$ . If any permutation of subset S of the variables does not change the function f, then f is **partially symmetric**.

**Definition 3.5.3.** The **elementary symmetric functions** of n variables are

$S_i^n = 1$  iff exactly *i* out of *n* inputs are equal to 1. Let  $A \subseteq \{0, 1, ..., n\}$ . A symmetric function  $S_A^n$  is defined as follows:

$$S_A^n = \bigvee_{i \in A} S_i^n.$$

Example 3.5.1.  $f(x_1, x_2, x_3) = x_1 x_2 x_3 \vee x_1 \bar{x}_2 \bar{x}_3 \vee \bar{x}_1 x_2 \bar{x}_3 \vee \bar{x}_1 \bar{x}_2 x_3$  is a totally symmetric function. f = 1 when all the variables are 1, or when only one variable is 1. Thus, f can be written as  $S_1^3 \vee S_3^3 = S_{\{1,3\}}^3$ .

**Theorem 3.5.1.** An arbitrary n-variable symmetric function f is uniquely represented by elementary symmetric functions  $S_0^n, S_1^n, \ldots, S_n^n$  as follows:

$$f = \bigvee_{i \in A} S_i^n = S_A^n$$

, where  $A \subseteq \{0, 1, \dots, n\}$ .

**Lemma 3.5.1.** There are  $2^{n+1}$  symmetric functions of n variables.

**Definition 3.5.4.** Let SB(n, k) be the *n*-variable symmetric function represented by the EXOR sum of all the products consisting of k positive literals:

$$SB(n,0) = 1,$$

$$SB(n,1) = \sum x_i,$$

$$SB(n,2) = \sum x_i x_j,$$

$$SB(n,3) = \sum x_i x_j x_k,$$

$$\dots$$

$$SB(n,n) = x_1 x_2 \dots x_n.$$

Example 3.5.2.

$$SB(4,1) = x_1 \oplus x_2 \oplus x_3 \oplus x_4.$$

$$SB(4,2) = x_1x_2 \oplus x_1x_3 \oplus x_1x_4 \oplus x_2x_3 \oplus x_2x_4 \oplus x_3x_4.$$

SB(n,k) has been used as a benchmark function for an AND-EXOR logic minimizer [104]. The following two lemmas were derived by Komamiya [50] and reformulated by the author [110].

**Lemma 3.5.2.** Let  $x_1, x_2, ..., x_n$  be binary variables and r be an integer defined by  $r = x_1 + x_2 + \cdots + x_n$ , where + is an ordinary integer addition. Let the binary representation of r be

$$(y_k, y_{k-1}, \dots, y_1, y_0)_2, y_j \in \{0, 1\} (j = 0, 1, \dots, k).$$

In other words,

$$x_1 + x_2 + \dots + x_n = 2^k y_k + 2^{k-1} y_{k-1} + \dots + 2y_1 + y_0.$$

Then,

$$y_i = SB(n, 2^i).$$

**Lemma 3.5.3.** Let  $0 \le k_1 < k_2 < \dots < k_s$ , and  $2^{k_1} + 2^{k_2} + \dots + 2^{k_s} \le n$ . Then,

$$\bigwedge_{i=1}^{s} SB(n, 2^{k_i}) = SB\left(n, \sum_{i=1}^{s} 2^{k_i}\right).$$

*Example 3.5.3.*

$$SB(7, 1)SB(7, 2)SB(7, 4) = SB(7, 7),$$

$SB(4, 1)SB(4, 2) = SB(4, 3),$

$SB(6, 2)SB(6, 4) = SB(6, 6).$

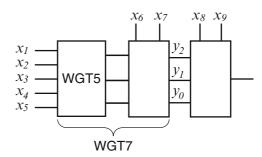

**Definition 3.5.5.** WGTn is an n-input  $\lceil \log_2(n+1) \rceil$ -output function. It counts the number of 1's in the inputs and represents it as a binary number.

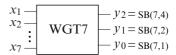

**Fig. 3.14** WGT7

$$x_1$$

$x_2$

$\vdots$

$w_{GT7}$

$y_2 = s_{B(7,4)}$

$y_1 = s_{B(7,2)}$

$y_0 = s_{B(7,1)}$

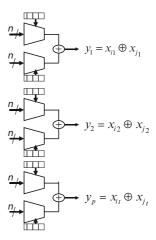

By Lemma 3.5.2, WGT*n* produces  $SB(n, 2^i)$ ,  $(i = 0, 1, 2, ..., \lceil \log_2(n+1) \rceil - 1)$ , where  $\lceil a \rceil$  denotes the smallest integer greater than or equal to a.

Example 3.5.4. WGT7 has  $x_1, x_2, ..., x_7$  as inputs and  $y_2, y_1, y_0$  as outputs (Fig. 3.14). By Lemma 3.5.2, we have

$$y_2 = SB(7,4) = \underbrace{\sum_{i < j < k < l}}_{i < j < k < l} x_i x_j x_k x_l$$

$$y_1 = SB(7,2) = \underbrace{\sum_{i < j}}_{i < j} x_i x_j$$

$$y_0 = SB(7,1) = \underbrace{\sum_{i = 1}^{7}}_{i = 1} x_i$$

WGT 7 is also called as rd73.

The following is an expansion method for symmetric functions using SB(n,k) functions:

**Theorem 3.5.2.** An arbitrary n-variable symmetric function f is represented by  $y_i = SB(n, 2^i)$ , (i = 0, 1, 2, ..., t) as follows:

$$f = \sum_{(a_0, a_1, \dots, a_t)} g(a_0, a_1, \dots, a_t) y_0^{a_0} y_1^{a_1} \dots y_t^{a_t},$$

where  $g(a_0, a_1, ..., a_t)$  is 0 or 1, and  $t = \lceil \log_2(n+1) \rceil - 1$ .

*Proof.* A symmetric function f depends only on the number of 1's in the inputs. Since WGTn counts the number of 1's in the input, we can represent f as a function of  $y_0, y_1, ..., y_t$ .

Example 3.5.5. A 7-variable symmetric function  $S_0^7$  can be represented as

$$S_0^7 = \bar{y}_2 \bar{y}_1 \bar{y}_0$$

=  $\overline{SB(7,4)} \cdot \overline{SB(7,2)} \cdot \overline{SB(7,1)}$ .

Note that the binary representation of 0 is (0,0,0). Similarly,  $S_3^7$  is represented as

$$S_3^7 = \bar{y}_2 y_1 y_0$$

=  $\overline{SB(7,4)} \cdot SB(7,2) \cdot SB(7,1)$ .

Thus,  $S_{\{0,3\}}^7$  is represented as

$$S_{\{0,3\}}^7 = S_0^7 \oplus S_3^7 = \bar{y}_2 \bar{y}_1 \bar{y}_0 \oplus \bar{y}_2 y_1 y_0$$

=  $\bar{y}_2(\bar{y}_1 \bar{y}_0 \oplus y_1 y_0) = \bar{y}_2(y_1 \oplus \bar{y}_0)$

=  $\overline{SB(7,4)} \cdot (SB(7,2) \oplus \overline{SB(7,1)}).$

#### 3.6 Technology Mapping

Logic synthesis using embedded memories can be considered as a special case of FPGA design, where the number of LUT inputs is large. Most existing methods use LUT-based technology mapping [33]. That is, given a combinational logic circuit, they partition it into sub-circuits depending on at most *K* variables [22,53,153]. This method was originally used for the LUT-based FPGA synthesis. Here, we introduce the basic idea.

**Definition 3.6.1.** [23, 57, 71] A combinational network can be converted into a DAG, where each node represents a logic gate (LUT), a **primary input** (PI), or a **primary output** (PO). When the output of the gate i is an input of gate j, a directed edge (i, j) exists. input(v) denotes the set of nodes which are fanins of gate v. output(v) denotes the set of nodes which are fanouts of gate v. A **cone** at v, denoted as  $C_v$ , is a subgraph consisting of v and its non-PI predecessors such that any path connecting a node in  $C_v$  and v lies entirely in  $C_v$ . Node v is the **root** of the cone. The **fanin size** of a cone is the number of input edges. A cone with K input edge is K-**feasible** and can be implemented with a K-LUT.

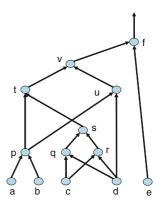

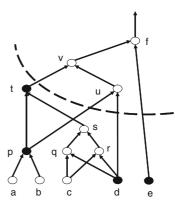

*Example 3.6.1.* In Fig. 3.15, a, b, c, d, e are PIs, and f denotes the PO. The cone of v consists of internal nodes v, t, u, s, p, q, and r. The fanin size of  $C_v$  is four. Thus,  $C_v$  is 4-feasible and can be implemented by a 4-LUT.

**Fig. 3.15** Example of directed acyclic graph

**Fig. 3.16** Example of 4-feasible cut-set

**Definition 3.6.2.** Given a network N with a source s and a sink t, a **cut**  $(\mathcal{N}_1, \mathcal{N}_2)$  is a partition of the nodes in the network such that  $s \in \mathcal{N}_1$ ,  $t \in \mathcal{N}_2$  and no nodes in  $\mathcal{N}_2$  provide input to any node in  $\mathcal{N}_1$ . A **cut-set** of a cut is the set of all nodes v such that  $v \in \mathcal{N}_1$ , and v drives a node in  $\mathcal{N}_2$ . If the size of a cut-set is no more than K, then the cut is K-feasible. A **fanout-free cone** (FFC) at v, denoted  $FFC_v$ , is a cone of v, with output edge only originating from the root of the cone. A **maximum fanout free cone** (MFFC) is an FFC that maximizes the number of nodes contained in the FFC.

Example 3.6.2. In Fig. 3.16, let a be a source, and f be a sink. The set of nodes is partitioned into  $\mathcal{N}_1 = \{a, b, c, d, e, p, q, r, s, t\}$  and  $\mathcal{N}_2 = \{u, v, f\}$ . The cut-set of the cut  $(\mathcal{N}_1, \mathcal{N}_2)$  is  $\{t, p, d, e\}$ . It is 4-feasible. The MFFC of f is  $\{p, q, r, s, t, u, v, f\}$ . This is because a cone includes only non-PI nodes, by Definition 3.6.2. If the output of f is connected to an other output, then MMFC of f would be  $\{u, v, f\}$ .

In a technology mapping algorithm, usually, a given circuit is converted into an equivalent two-input network. If the DAG is represented as a set of trees, then the area minimization problem can be solved optimally using dynamic programming [47]. Unfortunately, most circuits have non-tree structure: There exist many fanouts and reconvergence. If the circuit is decomposed into a set of MFFCs, then it can also be solved optimally. In the approach of [22], the circuit is first mapped into LUTs using the best available algorithm. Then, it extracts large single-output and multiple-output fanout-free logic blocks and covers them entirely or partially by embedded memories. Since these design methods start from existing circuits, the quality of the solutions are not so good [57]. Improvements for technology mapping are shown in [71]. Especially, an efficient method to enumerate all the cuts up to K = 6 [71] and a method to compute useful cuts for any number of inputs [72]. In this book, the major tool for the memory-based design is a functional decomposition, so we will not go into the detail of the method.

3.8 Remarks 23

**Table 3.1** Approximation error for 1 - x

| х     | 1-x   | $e^{-x}$   | Error(x)   |

|-------|-------|------------|------------|

| 0.001 | 0.999 | 0.99900050 | 0.00000050 |

| 0.010 | 0.990 | 0.99004983 | 0.00005034 |

| 0.100 | 0.900 | 0.90483742 | 0.00537491 |

| 0.200 | 0.800 | 0.81873075 | 0.02341344 |

## 3.7 The Mathematical Constant *e* and Its Property

**Definition 3.7.1.** The mathematical constant e is defined as

$$e = \lim_{n \to \infty} \left( 1 + \frac{1}{n} \right)^n.$$

**Lemma 3.7.1.** When 0 < x << 1, 1 - x can be approximated by  $e^{-x}$ .

*Proof.* The Taylor expansion of a function f(x) is

$$f(x) = f(0) + \frac{x}{1!}f^{(1)}(0) + \frac{x^2}{2!}f^{(2)}(0) + \frac{x^3}{3!}f^{(3)}(0) + \dots + \frac{x^k}{k!}f^{(k)}(0) + \dots$$

Thus,  $e^x$  can be expanded as

$$e^x = 1 + x + \frac{x^2}{2!} + \frac{x^3}{3!} + \frac{x^4}{4!} + \cdots$$

When x is small, we need only to consider up to the second term, and we have

$$e^{-x} \simeq 1 - x$$

.

Consider the approximation error of Lemma 3.7.1:

Error(x) =

$$\frac{e^{-x} - (1 - x)}{1 - x}$$

.

Table 3.1 shows that when 0 < x < 0.1, the approximation error is quite small. Lemma 3.7.1 will be extensively used for the calculation of approximate probability in Chaps. 9, 10, and 11.

## 3.8 Remarks

Functional decomposition is the key technique in the memory-based logic synthesis. It efficiently represents a given Boolean function with reduced total amount of memory. Most Boolean functions do not have any functional decomposition [109]. However, practical functions often have functional decompositions. Thus, an

attempt to find functional decompositions is, in many cases, rewarding. Ashenhurst decompositions can be efficiently found by BDDs [10,60]. However, as for Curtis decomposition, no efficient methods are known. Some heuristic methods are known [59,147]. Excellent surveys on FPGA logic synthesis include [20,78,103].

### **Problems**

**3.1.** Using the definition of SB(n,k), verify the following equation:

$$SB(4,1) \cdot SB(4,2) = SB(4,3).$$

**3.2.** Show that most  $2^{2^k+2^{n-k+1}}$  functions have Ashenhurst decompositions of the form

$$f(X_1, X_2) = g(h(X_1), X_2),$$

where

$$X_1 = (x_1, x_2, \dots, x_k)$$

and  $X_2 = (x_{k+1}, x_{k+2}, \dots, x_n)$ .

**3.3.** Show that most  $2^{m2^k+2^{n-k+m}}$  functions have Curtis decompositions of the form

$$f(X_1, X_2) = g(h_1(X_1), h_2(X_1), \dots, h_m(X_1), X_2),$$

where

$$X_1 = (x_1, x_2, \dots, x_k)$$

and  $X_2 = (x_{k+1}, x_{k+2}, \dots, x_n)$ .

**3.4.** Let f(X) be the function that counts the number of 1's in the inputs.

$${0,1}^5 \rightarrow {0,1,2,3,4,5}.$$

That is,  $f(\vec{a})$  denotes the number of 1's in  $\vec{a}$ . Write the decomposition chart and obtain the column multiplicity of the decomposition  $(X_1, X_2)$ , where  $X_1 = (x_1, x_2, x_3)$  and  $X_2 = (x_4, x_5)$ .

- **3.5.** How many functions of n variables with weight k exist?

- **3.6.** Represent the symmetric function of 9 variables:  $S_{\{3,4,5,6\}}^9$  by

$$y_3 = SB(9, 8),$$

$y_2 = SB(9, 4),$

$y_1 = SB(9, 2),$  and

$y_0 = SB(9, 1).$

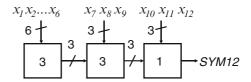

**3.7.** SYM12 is a symmetric function of 12 variables that is 1 iff the number of 1's in the inputs is between 4 and 8. Consider the decomposition of the function  $SYM12 = f(X_1, X_2)$ , where  $X_1 = (x_1, x_2, ..., x_9)$  and  $X_2 = (x_{10}, x_{11}, x_{12})$ . Show that the column multiplicity of the function with respect to  $(X_1, X_2)$  is  $\mu_9 = 8$ .

# **Chapter 4 MUX-Based Synthesis**

This chapter shows a universal method to realize an n-variable function using multiplexers (MUXs) and look up tables (LUTs). It also derives upper bounds on the number of LUTs to realize an n-variable function. Such bounds are useful to estimate the number of LUTs needed to realize a given function when we only know the number of the input variables n.

## 4.1 Fundamentals of MUX

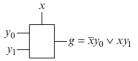

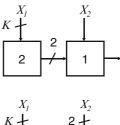

**Definition 4.1.1.** A **multiplexer** with a single control input (1-MUX) is the selection circuit shown in Fig. 4.1. It performs the logical operation

$$g(x, y_0, y_1) = \bar{x}y_0 \vee xy_1.$$

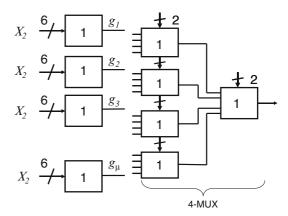

A **t-MUX** is shown in Fig. 4.2. It is a multiplexer with t control inputs  $(x_1, \ldots, x_t)$  and  $2^t$  data inputs  $(y_0, y_1, \ldots, y_{2^t-1})$ . Let  $g(x_1, \ldots, x_t, y_0, y_1, \ldots, y_{2^t-1})$  be the output function. Then,  $g = y_a$  when the decimal representation of the control input  $(x_1, \ldots, x_t)$  is a. That is, when the control input is  $(0, 0, \ldots, 0)$ , the top data input  $y_0$  drives the output. When the control input is  $(0, 0, \ldots, 1)$ , the second data input  $y_1$  drives the output. Also, when the control input is  $(1, 1, \ldots, 1)$ , the last data input  $y_{2^t-1}$  drives the output.

An t-MUX can be realized using 1-MUXs.

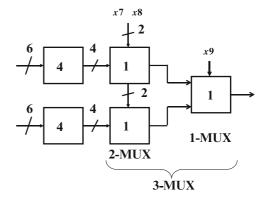

Example 4.1.1. A 3-MUX is realized with  $2^3 - 1 = 7$  modules of 1-MUXs, as shown in Fig. 4.3.

**Lemma 4.1.1.** A t-MUX is realized by using  $2^t - 1$  modules of 1-MUXs.

*Proof.* This can easily be done by mathematical induction.

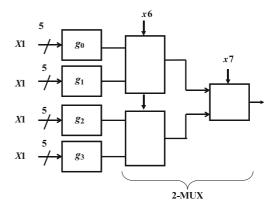

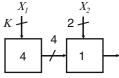

When  $K \ge 4$ , a 2-MUX can be realized with one or two K-LUTs.

П

Fig. 4.1 1-MUX

**Fig. 4.2** *t*-MUX

**Fig. 4.3** 3-MUX realized by 1-MUXs

**Lemma 4.1.2.** [57, 73] A 2-MUX can be realized by two 4-LUTs as shown in Fig. 4.4, where

$$g = (y_0 \bar{x}_2 \vee y_1 x_2) \bar{x}_1 \vee x_1 x_2$$

and

$$h = g\bar{x}_1 \vee (y_2\bar{g} \vee y_3g)x_1.$$

*Proof.* When  $x_1=0$ , we have  $g=y_0\bar{x}_2\vee y_1x_2$  and h=g. Thus,  $h=y_0\bar{x}_2\vee y_1x_2$ . When  $x_1=1$ , we have  $g=x_2$  and  $h=y_2\bar{g}\vee y_3g$ . Thus,  $h=y_2\bar{x}_2\vee y_3x_2$ . Therefore, the circuit realizes the 2-MUX function.

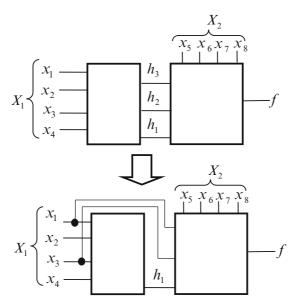

Figure 4.4 shows a nondisjoint decomposition. A method to derive this decomposition is considered in Chap. 6.

When K = 5, a 2-MUX can be realized by two 5-LUTs as shown in Fig. 4.5.

When K = 6, a 2-MUX can be realized by a single 6-LUT instead of using three 1-MUXs as shown in Fig. 4.6.

**Fig. 4.4** 2-MUX realized by 4-LUTs

**Fig. 4.5** 2-MUX realized by 5-LUTs

**Fig. 4.6** 2-MUX realized by a 6-LUT

## 4.2 MUX-Based Realization

**Theorem 4.2.1.** An arbitrary n-variable function can be represented as follows:

$$f(X_1, X_2) = \bigvee_{i \in P} g_i(X_1) X_2^i,$$

where  $X_1 = (x_1, x_2, ..., x_k)$  and  $X_2 = (x_{k+1}, x_{k+2}, ..., x_n)$ ,  $P = \{0, 1, ..., 2^{n-k} - 1\}$ , and the OR is performed with respect to  $2^{n-k}$  elements.

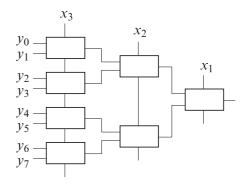

**Fig. 4.7** Realization of an arbitrary 7-variable function using 5-LUTs

Example 4.2.1. Consider the realization of a 7-variable function  $f(X_1, X_2)$ , where  $X_1 = (x_1, x_2, \dots, x_5)$ , and  $X_2 = (x_6, x_7)$ . f is expanded into a sum of four products:

$$f(X_1, X_2) = \bigvee_{i=0}^{3} g_i(X_1) X_2^i$$

=  $g_0(X_1) X_2^0 \vee g_1(X_1) X_2^1 \vee g_2(X_1) X_2^2 \vee g_3(X_1) X_2^3$ .

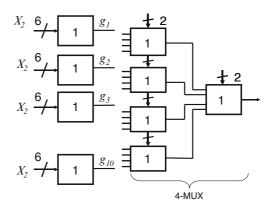

As shown in Fig. 4.7, a 2-MUX can be realized by using three 1-MUXs. The top LUT in the left most column realizes  $g_0$ , which is selected when  $(x_6, x_7) = (0, 0)$ . The second LUT in the leftmost column realizes  $g_1$ , which is selected when  $(x_6, x_7) = (0, 1)$ . Other LUTs are derived similarly.

**Theorem 4.2.2.** When  $3 \le K \le n$ , an arbitrary n-variable function is realized by using at most  $2^{n-K} - 1$  modules of 1-MUXs and  $2^{n-K}$  modules of K-LUTs.

*Proof.* Consider the expansion of Theorem 4.2.1. First, realize an (n-K)-MUX by using 1-MUXs. By Lemma 4.1.1, we need  $2^{n-K}-1$  modules of 1-MUXs. Next, by connecting  $g_i(X_1)$  to the data inputs of the (n-K)-MUX, realize an arbitrary n-variable function. To realize  $g_i(X_1)$   $(i=0,1,\ldots,2^{n-K}-1)$ , we use  $2^{n-k}$  modules of K-LUTs.

Next, consider several special cases.

**Lemma 4.2.1.** An arbitrary function of n = K + 1 variables can be realized with at most three K-LUTs, where  $K \ge 3$ .

*Proof.* Let  $X_1 = (x_1, x_2, \dots, x_K)$  and  $X_2 = (x_{K+1})$ . Then, the function can be represented as

$$f(X_1, X_2) = \bar{x}_{K+1} f(X_1, 0) \vee x_{K+1} f(X_1, 1).$$

**Fig. 4.8** Realization of a k+1 variable function

**Fig. 4.9** Realization of a k+2 variable function

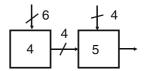

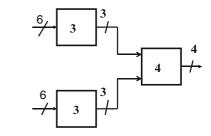

Thus, f can be realized by three K-LUTs as shown in Fig. 4.8. Note that the left cell realizes  $f(X_1, 0)$  and  $f(X_1, 1)$ , while the right cell works as a selector (1-MUX) to realize f. The integer in a cell denotes the number of LUTs to realize the cell. This is an LUT cascade, which will be explained in the next chapter.

**Lemma 4.2.2.** An arbitrary function of n = K + 2 variables can be realized with at most five K-LUTs, where  $K \ge 6$ .

*Proof.* Let  $X_1 = (x_1, x_2, \dots, x_K)$  and  $X_2 = (x_{K+1}, x_{K+2})$ . Then, the function can be represented as

$$f(X_1, X_2) = \bar{x}_{k+1} \bar{x}_{K+2} f(X_1, 0, 0) \vee \bar{x}_{K+1} x_{K+2} f(X_1, 0, 1) \vee x_{K+1} \bar{x}_{K+2} f(X_1, 1, 0) \vee x_{K+1} x_{K+2} f(X_1, 1, 1).$$

Thus, f can be realized by five K-LUTs, as shown in Fig. 4.9. Note that the left cell generates  $f(X_1, 0, 0)$ ,  $f(X_1, 0, 1)$ ,  $f(X_1, 1, 0)$ , and  $f(X_1, 1, 1)$ , while the right cell serves as a selector (2-MUX) to realize f. Figure 4.9 can be considered as a simplified representation of Fig. 4.7.

**Theorem 4.2.3.** [110] The number of 6-LUTs to realize an arbitrary n-variable function  $(n \ge 6)$  f is:

- $(2^{n-4}-1)/3$  or less, when n is even.

- $(2^{n-4}+1)/3$  or less, when n is odd.

*Proof.* Case 1: n is even (n = 2r):

We realize the function f in the form of Theorem 4.2.1, where K = 6. First, realize a (n - 6)-MUX by using 2-MUXs. This requires

$$1 + 4 + \dots + 4^{\frac{n-6}{2}-1} = 1 + 4 + \dots + 4^{r-4} = \frac{4^{r-3} - 1}{4 - 1}$$

П

6-LUTs. Next, realize  $g_i(X_1)$  ( $i = 0, 1, ..., 2^{n-k} - 1$ ). This requires  $4^{r-3}$  modules of 6-LUTs. So, the total number of 6-LUTs is

$$\frac{4^{r-3}-1}{3}+4^{r-3}=\frac{4^{r-2}-1}{3}=\frac{2^{n-4}-1}{3}.$$

Case 2: n is odd (n = 2r + 1):

The function f can be expanded into the form

$$f(X_1, x_n) = \bar{x}_n g_0(X_1) \vee x_n g_1(X_1), \tag{4.1}$$

where  $X_1 = (x_1, x_2, ..., x_{n-1})$ . Since  $g_i(X_1)$  (i = 0, 1) are functions with 2r variables, they can be realized by  $(4^{r-2} - 1)/3$  modules of 6-LUTs. To realize the expansion (4.1), we use a 1-MUX. Thus, the total number of 6-LUTs to realize f is

$$2 \cdot \frac{4^{r-2} - 1}{3} + 1 = \frac{2 \cdot 4^{r-2} + 1}{3} = \frac{2^{n-4} + 1}{3}.$$

Example 4.2.2. The number of 6-LUTs to realize an *n*-variable function is:

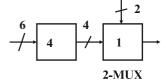

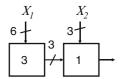

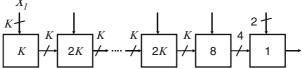

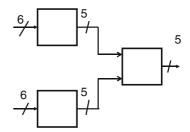

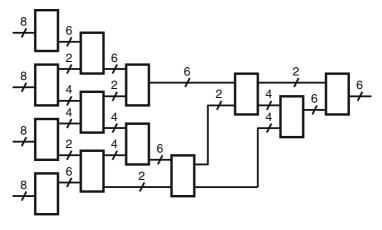

- 5 or less, when n = 8. In this case,  $g_i(X_1)$  (i = 0, 1, 2, 3) are realized by four modules of 6-LUTs, while the 2-MUX is realized by a single 6-LUT, as shown in Fig. 4.10. In the figure, the numbers in the squares denote the numbers of necessary LUTs.

- 11 or less, when n = 9. In this case,  $g_i(X_1)$  (i = 0, 1, 2, ..., 7) are realized by 8 modules of 6-LUTs, while the 3-MUX is realized by three 6-LUTs as shown in Fig. 4.11.

- 21 or less, when n = 10. In this case,  $g_i(X_1)$  (i = 0, 1, 2, ..., 15) are realized by 16 modules of 6-LUTs, while the 4-MUX is realized by using five 6-LUTs as shown in Fig. 4.12.

**Theorem 4.2.4.** Consider the function  $f(X_1, X_2)$ , where  $X_1 = (x_1, x_2, x_3, x_4)$  and  $X_2 = (x_5, x_6, ..., x_{K+3}, x_{K+4})$ . Let  $\mu$  be the column multiplicity of the decomposition  $f(X_1, X_2)$ , where  $X_1$  denotes the bound variables. Then, f can be realized with at most  $\mu + 5$  modules of K-LUTs, where  $K \ge 6$ .

*Proof.* The function  $f(X_1, X_2)$  can be expanded as

$$f(X_1, X_2) = g_0(\vec{a}_0, X_2) \vee g_1(\vec{a}_1, X_2) \vee g_2(\vec{a}_2, X_2) \vee \cdots \vee g_{15}(\vec{a}_{15}, X_2),$$

**Fig. 4.10** Realization of an arbitrary 8-variable function using 6-LUTs

4.3 Remarks 31

**Fig. 4.11** Realization of an arbitrary 9-variable function using 6-LUTs

**Fig. 4.12** Realization of an arbitrary 10-variable function using 6-LUTs

where  $\vec{a}_0 = (0, 0, 0, 0)$ ,  $\vec{a}_1 = (0, 0, 0, 1)$ ,  $\vec{a}_2 = (0, 0, 1, 0)$ ,..., and  $\vec{a}_{15} = (1, 1, 1, 1)$ . Thus,  $f(X_1, X_2)$  can be realized as the circuit shown in Fig. 4.12. Since the column multiplicity is  $\mu$ , the number of different column functions  $g_i(\vec{a}_i, X_2)$  is  $\mu$ . So, in Fig. 4.12, the LUTs producing the same functions can be shared, and only  $\mu$  LUTs are sufficient to produce  $g_i(\vec{a}_i, X_2)$ .

## 4.3 Remarks

This chapter derived the number of 6-LUTs to realize an n-variable logic function. The number of required LUTs increases exponentially with n. So, the MUX-based design is only practical for the functions with a small number of inputs. However, the MUX-based method sometimes produces circuits with fewer LUTs [134] than existing methods [73, 76], in particular, for random logic functions. In this chapter, we represented the function by Shannon expansion. However, if we use

**pseudo-Kronecker expansion** [110], we can reduce the number of LUTs by 23% [107]. In the pseudo-Kronecker expansion, we can select one from 840 possible expansions to reduce the number of LUTs.

#### **Problems**

- **4.1.** Consider a 10-variable function f(X). Let  $(X_1, X_2)$  be a partition of the variables X, where  $X_1 = (x_1, x_2, x_3, x_4, x_5, x_6)$  and  $X_2 = (x_7, x_8, x_9, x_{10})$ . Assume that  $\mu_6 = 16$ . That is, the column multiplicity of the decomposition chart is 16. Show that f can be realized with at most nine 6-LUTs.

- **4.2.** Let  $(X_1, X_2)$  be the partition of the variables X, where  $X_1 = (x_1, x_2, x_3, x_4)$  and  $X_2 = (x_5, x_6, x_7, x_8, x_9, x_{10})$ . Suppose that the column multiplicity is 10, i.e.,  $\mu_4 = 10$ . Then, show that f can be realized with at most 15 copies of 6-LUTs.

- **4.3.** Show that an arbitrary logic function can be represented as

$$f(x_1, x_2, Y) = g_0(Y) \oplus x_1 g_1(Y) \oplus x_2 g_2(Y) \oplus x_1 x_2 g_3(Y). \tag{4.2}$$

This is the **Reed–Muller expansion**. Consider the Shannon expansion:

$$f(x_1, x_2, Y) = \bar{x}_1 \bar{x}_2 f_0(Y) \oplus \bar{x}_1 x_2 f_1(Y) \oplus x_1 \bar{x}_2 f_2(Y) \oplus x_1 x_2 g_3(Y). \tag{4.3}$$

Represent  $g_0(Y)$ ,  $g_1(Y)$ ,  $g_2(Y)$ , and  $g_3(Y)$  by  $f_0(Y)$ ,  $f_1(Y)$ ,  $f_2(Y)$ , and  $f_3(Y)$ .

**4.4.** Consider the function  $f(X_1, X_2)$ , where  $X_1 = (x_1, x_2, \dots, x_{2k})$  and  $X_2 = (x_{2k+1}, x_{2k+2}, \dots, x_{2k+6})$ . Let  $\mu$  be the column multiplicity of the decomposition  $f(X_1, X_2)$ , where  $X_1$  denotes the bound variables. Then, show that f can be realized with at most

$$\mu + \frac{4^k - 1}{3}$$

6-LUTs.

# Chapter 5

# **Cascade-Based Synthesis**

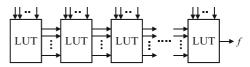

The previous chapter presented a multiplexer (MUX)-based realization. Although such a method is applicable to any n-variable function f, the number of LUTs necessary to realize f increases as  $O(2^n)$ . This chapter considers a cascade-based logic synthesis. A cascade-based realization is applicable to only a limited class of functions. However, functions with a small C-measure can be realized by cascade-based realizations with O(n) LUTs.

## 5.1 Functional Decomposition and LUT Cascade

Before considering the general case, we review special cases.

**Lemma 5.1.1.** An arbitrary function of n = K + 1 variables can be realized with at most three K-LUTs, where  $K \ge 3$ .

*Proof.* This is the same as Lemma 4.2.1.

**Lemma 5.1.2.** An arbitrary function of n = K + 2 variables can be realized with at most five K-LUTs, where  $K \ge 6$ .

*Proof.* This is the same as Lemma 4.2.2.

From the definition of a decomposition chart, we have the following:

**Theorem 5.1.1.** [8] Let  $\mu_k(n)$  be the column multiplicity of a decomposition chart of an n-variable logic function with k bound variables. Then,

$$\mu_k(n) \le \min\left\{2^k, 2^{2^{n-k}}\right\}.$$

When circuits are designed by LUTs, functions with smaller column multiplicities tend to have smaller realizations.

**Definition 5.1.1.** Let  $f(x_1, x_2, ..., x_n)$  be a logic function. The **profile** of the function f is the vector  $(\mu_1, \mu_2, ..., \mu_n)$ , where  $\mu_k$  denotes the column multiplicity of the decomposition chart for  $f(X_1, X_2)$ ,  $X_1 = (x_1, x_2, ..., x_k)$  and

П

$X_2 = (x_{k+1}, \dots, x_n)$ , assuming that the order of variables  $(x_1, x_2, \dots, x_n)$  is fixed. The **C-measure** of the function f is  $\max(\mu_1, \mu_2, \dots, \mu_n)$  and is denoted by  $\mu(f)$ .

Note that the order of the variables will affect the C-measure, but we choose the **natural order**  $(x_1, x_2, ..., x_n)$  of the input variables.

**Lemma 5.1.3.** Let f be an arbitrary n-variable function. Then,

$$\mu(f) \le \max_{k=1}^{n} \min \left\{ 2^{k}, 2^{2^{n-k}} \right\}.$$

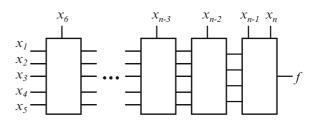

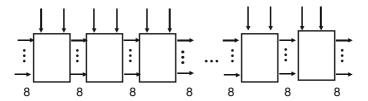

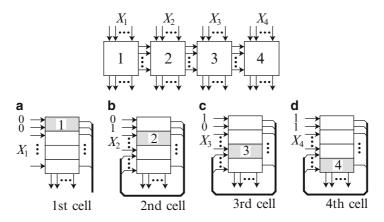

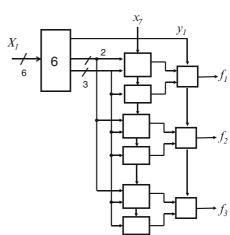

For any partition  $(X_1, X_2)$  of X, we have the decomposition shown in Fig. 5.1. By repeatedly applying functional decompositions to a given function  $f(X) = f(X_1, X_2, ..., X_s)$ , we have an **LUT cascade** [113] shown in Fig. 5.2. An LUT cascade consists of **cells**. The signal lines connecting adjacent cell are **rails**. A logic function with a small C-measure can be realized by a compact LUT cascade.

**Lemma 5.1.4.** [113] An arbitrary logic function f can be realized by an LUT cascade, whose cells have at most  $\lceil \log_2 \mu(f) \rceil + 1$  inputs, and at most  $\lceil \log_2 \mu(f) \rceil$  outputs, where  $\mu(f)$  is the C-measure of f.

**Lemma 5.1.5.** [127] In an LUT cascade that realizes an n-variable function f, let s be the number of cells;  $w = \lceil \log_2 \mu(f) \rceil$  be the maximum number of rails; K be the number of inputs to a cell;  $n \ge K + 1$ ; and  $K \ge \lceil \log_2 \mu(f) \rceil + 1$ . Then, an LUT cascade satisfying the following condition exists:

$$s = \left\lceil \frac{n - w}{K - w} \right\rceil. \tag{5.1}$$

*Proof.* From the design method of the LUT cascade, we have

$$K + (K - w)(s - 1) > n$$

.

Here, K on the left-hand side of the equality denotes the number of inputs of the leftmost LUT, and (K-w)(s-1) denotes the sum of inputs for the remaining (s-1)

**Fig. 5.1** Realization of a logic function by decomposition

Fig. 5.2 LUT cascade

**Fig. 5.3** Realization of a 9-variable function with C-measure not exceeding 8

LUTs. When the actual number of rails is smaller than w, we append dummy rails to make the number of rails w. From this, we have

$$s-1 \ge \frac{n-K}{K-w}$$

, and  $s \ge \frac{n-w}{K-w}$ .

Since s is an integer, we have (5.1). When this is the case, we can realize an LUT cascade for f having s cells with at most K inputs.

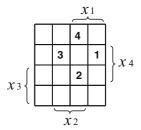

Example 5.1.1. Let  $f(X_1, X_2)$  be a 9-variable function, where  $X_1 = (x_1, x_2, \dots, x_6)$  and  $X_2 = (x_7, x_8, x_9)$ . Let  $\mu_6$  be the column multiplicity of the decomposition of f with respect to  $(X_1, X_2)$ . If  $\mu_6 \le 8$ , then  $f(X_1, X_2)$  can be realized with four 6-LUTs, as shown in Fig. 5.3. Note that the number of rails between two cells is  $\lceil \log_2 8 \rceil = 3$ , by Theorem 3.3.1. In many cases, the natural ordering of the input variables does *not* yield the smallest circuit. To check if  $\mu_6 \le 8$  for all arrangements of variables, we need to compute the column multiplicities for  $\binom{9}{6} = 84$  combinations of variables.

## Lemma 5.1.6. Consider a cascade consisting of K-LUTs.

- 1. When the number of the external input variables to the output LUT is one, the number of the rail inputs to the LUT is at most two.

- 2. When the number of the external input variables to the output LUT is two, the number of the rail inputs to the LUT is at most four.

*Proof.* We prove the second case only. The proof for the first case is similar. Let  $x_{n-1}$  and  $x_n$  be external input variables for the output LUT. Consider the decomposition chart, where the rail inputs  $X_1 = (x_1, x_2, \dots, x_{n-2})$  denotes the set of bound variables and the external input  $X_2 = (x_{n-1}, x_n)$  denotes the set of free variables. In this case, the column multiplicity is at most 16, since there exist at most  $2^{2^2} = 16$  different column functions by Theorem 5.1.1. Also by Theorem 3.3.1, the number of the rail inputs to the output LUT is at most four.

### 5.2 Number of LUTs to Realize General Functions

As for realizations by 6-LUTs, we have the following:

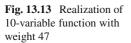

**Theorem 5.2.1.** The number of 6-LUTs needed to realize an arbitrary n-variable function with  $\mu(f) \le 32$  is 5n - 35 or less, where  $n \ge 8$ .

**Fig. 5.4** Realization with 6-LUTs

*Proof.* From Lemma 5.1.4, an arbitrary function with  $\mu(f) \leq 32$  can be realized by an LUT cascade, whose cells have at most  $\lceil \log_2 \mu \rceil + 1 = \log_2(32) + 1 = 6$  inputs, and  $w = \log_2(32) = 5$  outputs. Let K = 6. Then, from Lemma 5.1.5, the number of cells is at most  $\lceil \frac{n-w}{K-w} \rceil = \frac{n-5}{6-5} = n-5$ . Note that each cell except for the rightmost cell has at most 5 outputs. From Lemma 5.1.6, the second cell from the right has at most four outputs as shown in Fig. 5.4. So, the total number of cells is at most n-6. Note that the second cell from the right has 4 outputs, while the rightmost cell has just one output. Therefore, the total number of LUTs is at most 5(n-8)+4+1=5n-35.

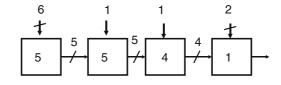

**Theorem 5.2.2.** The number of 6-LUTs needed to realize an arbitrary n-variable function with  $\mu(f) \le 16$  is 2n - 11 or less, where  $n \ge 8$ .

*Proof.* Let  $w = \log_2(16) = 4$  and K = 6. From Lemma 5.1.5, we have  $s \le \left\lceil \frac{n-w}{K-w} \right\rceil = \frac{n-4}{6-4} = \left\lceil \frac{n-4}{2} \right\rceil$ .

When n = 2r, each cell except for the rightmost cell has at most 4 outputs. So, the total number of LUTs is at most  $4 \times (\lceil \frac{n-4}{2} \rceil - 1) + 1 = 2(n-4) - 4 + 1 = 2n - 11$ .

When n = 2r + 1, by Lemma 5.1.6, the rightmost cell has one external input and at most two rail inputs, and the second cell from the right has at most two outputs. So, the total number of LUTs is at most  $4 \times (\lceil \frac{n-5}{2} \rceil - 1) + 2 + 1 = 2n - 11$ .  $\square$

**Theorem 5.2.3.** The number of 6-LUTs needed to realize an arbitrary n-variable function with  $\mu(f) \leq 8$  is n-5 or less when n=3r, and n-4 or less when  $n \neq 3r$ , where  $n \geq 8$ .

*Proof.* Let  $w = \log_2 8 = 3$  and K = 6. From Lemma 5.1.5, we have  $s \le \left\lceil \frac{n-w}{K-w} \right\rceil = \left\lceil \frac{n-3}{3} \right\rceil$ .

When n = 3r, each cell except for the rightmost cell has at most 3 outputs. So, the total number of LUTs is at most  $3 \times (\lceil \frac{n-3}{3} \rceil - 1) + 1 = (n-3) - 3 + 1 = n - 5$ .

When n = 3r + 1, the rightmost cell has one external input and at most two rail inputs, and the second cell from the rightmost one has at most 2 outputs. So, the total number of LUTs is at most  $3 \times (\lceil \frac{n-4}{3} \rceil - 1) + 2 + 1 = (n-4) - 3 + 3 = n - 4$ .

When n = 3r + 2, the rightmost cell has two external inputs. So, the total number of LUTs is at most  $3 \times (\lceil \frac{n-5}{3} \rceil - 1) + 3 + 1 = (n-5) - 3 + 4 = n - 4$ .

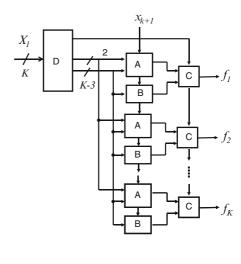

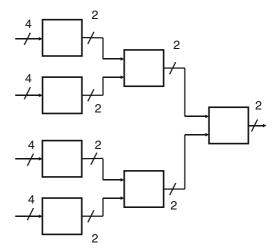

**Lemma 5.2.1.** The number of K-LUTs needed to realize a (K + 1)-variable k-output function F with  $\mu(F) < 2^{K-1} + 2^{K-3}$  is 3 K or less.

*Proof.* Consider the circuit shown in Fig. 5.5. Since the column multiplicity is at most  $2^{K-1} + 2^{K-3}$ , each pattern can be uniquely represented by a K-bit code. By using the leftmost cell D, generate K-bit codes that correspond to the column patterns. For the first  $2^{K-1}$  patterns, assign K-bit codes with the form (0, \*, \*, ..., \*), where \* denotes either 0 or 1. For the remaining  $2^{K-3}$  patterns, assign K-bit codes with the form (1, 0, 0, \*, \*, ..., \*). Cell A in Fig. 5.5 implements the function for the codes (0, \*, \*, ..., \*), while cell B implements the function for the codes (1, 0, 0, \*, ..., \*). Cell C is used for a selector, which is controlled by the most significant bit of the outputs of cell D. In this way, an arbitrary K output function can be realized by the circuit shown in Fig. 5.5. Note that cell C has three inputs. Cells C and C can be merged and realized by a C-input LUT. Thus, the total number of LUTs to implement this circuit is at most C.

**Theorem 5.2.4.** Let  $K \ge 6$  and  $n \ge K + 3$ . The number of K-LUTs to realize an n-variable function f with  $\mu(f) \le 2^{K-1} + 2^{K-3}$  is 2K(n-K) - 5K + 9 or less.

*Proof.* Consider the cascade shown in Fig. 5.6. Since  $\lceil \log_2 \mu \rceil \le K$ , the function can be realized by a cascade with at most K-rails. Also, by Lemma 5.2.1, each of the intermediate cells can be realized with at most 2K LUTs. By Lemma 5.1.6, the rightmost cell has at most four rail inputs and two external inputs. Also, note that the second cell from the right can be implemented with at most 8 LUTs. Note that

**Fig. 5.5** Realization of (K + 1)-variable K-output function

Fig. 5.6 Cascade realization in the proof

the number of outputs is at most four, and the number of inputs is K+1. We can prove that 8 LUTs is sufficient in a similar way to the proof of Lemma 5.2.1. The leftmost cell can be implemented with K LUTs. Thus, the total number of LUTs is K+2K(n-K-3)+9=2K(n-K)-5K+9.

#### Theorem 5.2.5.

- The number of 6-LUTs needed to realize an arbitrary n-variable function with  $\mu(f) \le 40$  is 12n 93 or less, where  $n \ge 9$ .

- The number of 7-LUTs needed to realize an arbitrary n-variable function with  $\mu(f) \le 80$  is 14n 124 or less, where  $n \ge 10$ .

- The number of 8-LUTs needed to realize an arbitrary n-variable function with  $\mu(f) \le 160$  is 16n 159 or less, where  $n \ge 11$ .

## 5.3 Number of LUTs to Realize Symmetric Functions

When the given function is symmetric, it can be realized more efficiently than a general function [106,112]. Efficient algorithms to detect symmetric functions exist, e.g., [70,91].

**Lemma 5.3.1.** Let f be a symmetric function of n-variables. Then,  $\mu(f) \le n+1$ .

*Proof.* Consider the partition of variables  $(X_1, X_2)$ , where  $X_1 = (x_1, x_2, \dots, x_k)$  and  $X_2 = (x_{k+1}, x_{k+2}, \dots, x_n)$ . Let  $\mu_k$  be the column multiplicity of the decomposition. Since f is symmetric, the column labels with the same weights have the same column patterns in the decomposition chart. Thus, the column multiplicity is at most k+1. From this, we have the lemma.

Example 5.3.1. Consider a symmetric function  $f(X_1, X_2)$ , where  $X_1 = (x_1, x_2, x_3)$  and  $X_2 = (x_4, x_5, x_6)$ . This is an example for k = 3. In this case, the number of columns is  $2^3 = 8$ . The column label with weight 0 is (0, 0, 0). The column labels with weight 1 are (1, 0, 0), (0, 1, 0), and (0, 0, 1). They have the same column functions. The column labels with weight 2 are (1, 1, 0), (1, 0, 1), and (0, 1, 1). They have the same column functions. And the column label with weight 3 is (1, 1, 1). Thus, the number of different column patterns is at most four.

In Chap. 7, tighter bounds are derived.

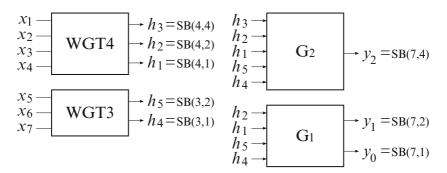

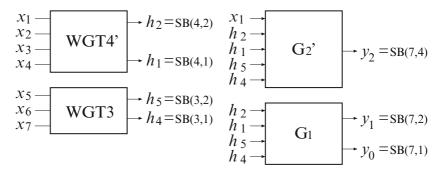

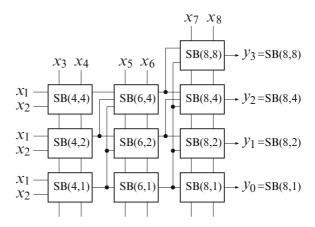

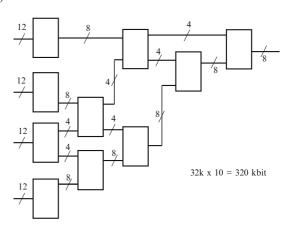

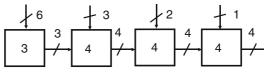

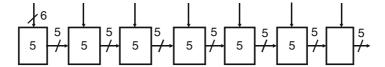

**Theorem 5.3.1.** The number of K-LUTs needed to realize an n-variable symmetric function is:

- 4 or less, when n = 9 and K = 6. Figure 5.3 shows the realization.

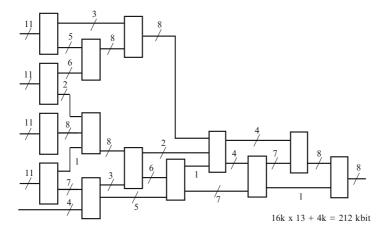

- 7 or less, when n = 12 and K = 6. Figure 5.7 shows the realization.

- 13 or less, when n = 15 and K = 6. Figure 5.8 shows the realization.

*Example 5.3.2.* Consider *SYM12* [110], a symmetric function of 12 variables. *SYM12* is 1 iff the number of 1's in the inputs is between 4 and 8.

**Fig. 5.7** Realization of a symmetric function of 12 variables by 6-LUTs

**Fig. 5.8** Realization of a symmetric function of 15 variables by 6-LUTs

**Fig. 5.9** SYM12 realized by 6-LUTs

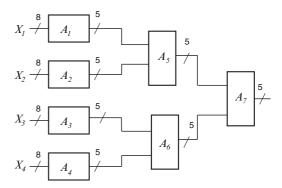

- 1. The column multiplicity of the function with respect to the bound set composed of K=6 variables is  $\mu_6=7$ . Thus, the number of rails between two blocks is  $\lceil \log_2 7 \rceil = 3$ .

- 2. We decompose the function with respect to the bound set:  $x_1, x_2, \dots, x_6$ . Realize the first cell using 6-LUTs, which corresponds to the leftmost cell in Fig. 5.9.

- 3. The remaining function has 12-6+3=9 variables. The bound variables for the second decomposition are three outputs of the leftmost cell, and  $x_7, x_8, x_9$ . In this case, the column multiplicity is  $\mu_9 = 8$  (Problem 3.8). Thus, the number of rails between two blocks is  $\lceil log_2 8 \rceil = 3$ .

- 4. We decompose the remaining function with the bound set: three outputs of the leftmost cell, and  $x_7$ ,  $x_8$ ,  $x_9$ . Realize the second cell using 6-LUTs, which corresponds to the middle cell in Fig. 5.9.

- 5. The remaining function has 9-6+3=6 variables. Since the number of remaining variables is equal to K=6, realize the function by a 6-LUT, which corresponds to the rightmost cell in Fig. 5.9.

- 6. In this way, *SYM12* is realized by 3 + 3 + 1 = 7 LUTs of 6-inputs. Note that this realization is different from that shown in Fig. 5.7.

## 5.4 Remarks

In this chapter, we showed a method to realize a given function by using a cascade of LUTs. This method is only applicable to the functions whose C-measures are small.

The C-measure of a logic function f is related to the size of its BDD. Sizes of BDDs for various classes of functions are considered in [154]. Classes of functions having small C-measures are considered in Chap. 7.

LSIs for LUT cascades have been fabricated [86–88]. This chapter is based on [134].

## **Problems**

- **5.1.** Compare the tree-type realization in Fig. 5.7 with the cascade realization in Fig. 5.9. Discuss their advantages and disadvantages.

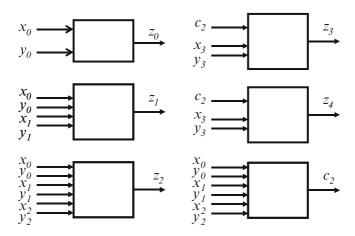

- **5.2.** Consider the 4-bit adder, where  $x_3, x_2, x_1, x_0$  and  $y_3, y_2, y_1, y_0$  denote the inputs, and  $z_4, z_3, z_2, z_1, z_0$  denote the outputs. Design the adder using an LUT cascade. Use 6-LUTs. Show the expression of the output function for each LUT.

- **5.3.** Design a 12-input 4-output circuit that counts the number of 1's in the inputs and represents this by a binary number (i.e., WGT12) by 6-LUTs.

- **5.4.** Consider a set of three functions  $f_i$  with 7 variables. Assume that  $\mu(f_i) \le 40$  for i = 1, 2, 3. Realize these functions by 6-LUTs, using the design method shown in the proof of Lemma 5.2.1.

- **5.5.** Let  $\mu_k(n)$  be the column multiplicity of a decomposition chart of an *n*-variable function with k bound variables. Show the following relations:

$$\mu_{k+1}(n) \le 2\mu_k(n)$$

$$\mu_{k-1}(n) \le \mu_k^2(n)$$

**5.6.** Enumerate the 8-variable functions whose C-measures are 32.

# **Chapter 6 Encoding Method**

This chapter shows a method to reduce the number of LUTs needed to realize logic functions with nonstandard encodings. In these encodings, intermediate variables in functional decomposition are represented with fewer variables. This method offers a way to find a nondisjoint decomposition.

## **6.1** Decomposition and Equivalence Class

**Definition 6.1.1.** Let  $f(X_1, X_2)$  be a logic function and  $(X_1, X_2)$  be a partition of X.  $|X_1|$  denotes the number of variables in  $X_1$ . Let  $B = \{0, 1\}$ . When  $n_1 = |X_1|$  and  $n_2 = |X_2|$ , an equivalence relation  $\sim$  on  $B^{n_1}$  is defined as follows:  $\vec{a} \sim \vec{b} \iff f(\vec{a}, X_2) = f(\vec{b}, X_2)$ , where  $\vec{a}, \vec{b} \in B^{n_1}$ . Let the equivalence classes of  $B^{n_1}$  be  $\Psi_0, \Psi_1, \ldots, \Psi_{\mu-1}$ . In this case,  $\mu$  is equal to the column multiplicity in the decomposition chart of f with the partition  $(X_1, X_2)$ .  $\Psi_i$  is also used to represent the corresponding logic function.

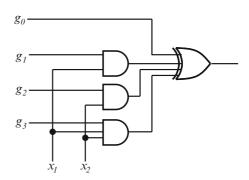

Example 6.1.1. Consider the function

$$f(X_1, X_2) = y_0 \bar{x}_1 \bar{x}_2 \vee y_1 \bar{x}_1 x_2 \vee y_2 x_1 \bar{x}_2 \vee y_3 x_1 x_2,$$

where  $X_1 = (x_1, x_2, y_0, y_1)$  and  $X_2 = (y_2, y_3)$ . The decomposition chart is shown in Fig. 6.1. The logic functions for the various equivalence classes are

$$\begin{split} &\Psi_0 = \bar{x}_1 \bar{x}_2 \bar{y}_0 \vee \bar{x}_1 x_2 \bar{y}_1 = \bar{x}_1 (\bar{x}_2 \bar{y}_0 \vee x_2 \bar{y}_1), \\ &\Psi_1 = x_1 x_2, \\ &\Psi_2 = x_1 \bar{x}_2, \text{ and} \\ &\Psi_3 = \bar{x}_1 \bar{x}_2 y_0 \vee \bar{x}_1 x_2 y_1 = \bar{x}_1 (\bar{x}_2 y_0 \vee x_2 y_1). \end{split}$$

Note that  $\Psi_0$  denotes the logic function for the equivalence class of the column vector  $(0,0,0,0)^t$ , where the symbol t denotes the transpose of the vector. Similarly,  $\Psi_1$  corresponds to  $(0,1,0,1)^t$ ,  $\Psi_2$  corresponds to  $(0,0,1,1)^t$ , and  $\Psi_3$  corresponds to  $(1,1,1,1)^t$ .

|                       |                       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | $x_1$       |

|-----------------------|-----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------|

|                       |                       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | $x_2$       |

|                       |                       | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | $y_0$       |

|                       |                       | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | $y_{\perp}$ |

| 0                     | 0                     | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | •           |

| 0                     | 1                     | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |             |

| 1                     | 0                     | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |             |

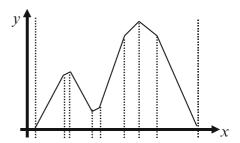

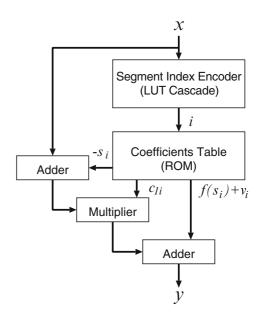

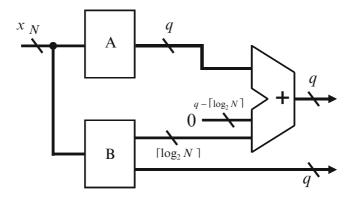

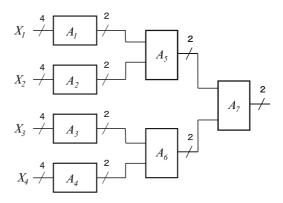

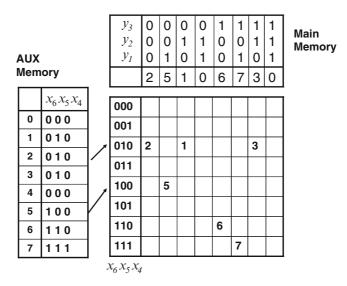

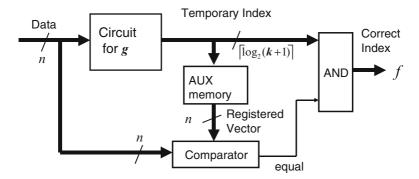

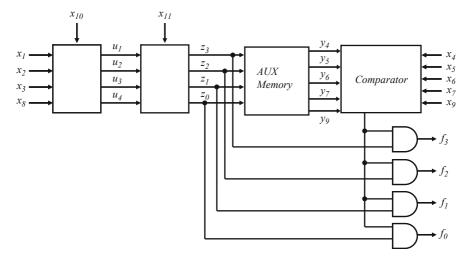

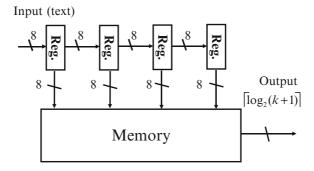

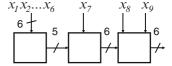

| 1                     | 1                     | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ĺ           |