# Lecture Notes in Computer Science

4899

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

# Karen Yorav (Ed.)

# Hardware and Software: Verification and Testing

Third International Haifa Verification Conference, HVC 2007 Haifa, Israel, October 23-25, 2007 Proceedings

Volume Editor

Karen Yorav IBM Haifa Labs Haifa University Campus Mount Carmel, Haifa, 31905, Israel E-mail: yorav@il.ibm.com

Library of Congress Control Number: 2008920255

CR Subject Classification (1998): D.2.4-5, D.2, D.3, F.3

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-77964-7 Springer Berlin Heidelberg New York ISBN-13 978-3-540-77964-3 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12225194 06/3180 5 4 3 2 1 0

#### **Preface**

This volume contains the proceedings of the 3rd Haifa Verification Conference (HVC 2007), which took place in Haifa during October 2007. HVC is a forum for researchers from both industry and academia to share and advance knowledge in the verification of hardware and software systems.

Academic research in verification is generally divided into two paradigms – formal verification and dynamic verification (testing). Within each paradigm, different algorithms and techniques are used for hardware and software systems. Yet, at their core, all of these techniques aim to achieve the same goal of ensuring the correct functionality of a complicated system. HVC is the only conference that brings together researchers from all four fields, thereby encouraging the migration of methods and ideas between domains.

With this goal in mind we established the HVC Award. This award recognizes a promising contribution to verification published in the last few years. It is aimed at developments that significantly advance the state of the art in verification technology and show potential for future impact on different verification paradigms. The winners of the HVC Award are chosen by an independent committee with experts from all fields of verification – both formal and dynamic, software and hardware. The winners of the 2007 HVC Award were Corina Păsăreanu and Willem Visser, for their work on combining static and dynamic analysis.

This year we received 32 submissions, out of which 15 were accepted after a thorough review conducted by the Program Committee (PC) and additional reviewers. Each paper was reviewed by at least three reviewers, sometimes more. PC members who submitted papers were not involved in any way in the review, discussion, or decision regarding their paper. The chosen papers were presented during the 3-day conference, along with keynote and invited presentations. These proceedings include reviewed papers as well as the extended abstracts of invited talks. In addition, we held a full-day tutorial titled: "Verification 101—The Basics of Hardware Verification and Software Testing." The tutorial was designed for non-experts who want to know what verification is all about and for people with knowledge in one aspect of verification (e.g., software testing) who wanted to become familiar with other aspects (e.g., formal verification). The goal was to supply the non-expert with the tools needed to better understand the talks that were later presented at the conference. The tutorial was hosted by our sponsor, the Caesarea Rothschild Institute (CRI) at the University of Haifa.

Attendance at the conference was very high, with more than 250 participants from 12 countries (Austria, Canada, Czech Republic, France, Germany, India, Israel, The Netherlands, Russia, Switzerland, UK, and USA). Thanks to sponsorship from Cadence Israel, we were able to offer student travel grants, thus enabling PhD students to travel to the conference to present their work.

I would like to thank the Organizing Committee, the HVC Award Committee, the Program Committee, and the authors of all submitted papers for their contribution to the high quality of this year's event. Thank you to the invited speakers who travelled from afar and made the conference that much more interesting: Bob Bentley, Aarti Gupta, Alan Hu, Bob Kurshan, Corina Păsăreanu, Wolfgang Roesner, and Andreas Zeller. Many thanks to Avi Ziv, Cindy Eisner, and Shmuel Ur for the excellent tutorial. Special thanks to Vered Aharon for doing an excellent job with the logistics of the conference and to all the people at IBM who put in time and energy to make this event a success: Tamar Dekel, Ephrat Elgarisi, Ruth Elnekave, Ettie Gilead, Yair Harry, Yael Hay-Karesenty, Chani Sacharen. Last but not least, I would like to thank our generous sponsors, and especially Amos Ziv from Cadence Israel and Martin Golumbic from CRI for all their help.

October 2007 Karen Yorav

# Organization

# Conference and Program Chair

Karen Yorav IBM Haifa Research Lab, Israel

# Organizing Committee

| Sharon Barner    | IBM Haifa Research Lab, Israel |

|------------------|--------------------------------|

| David Bernstein  | IBM Haifa Research Lab, Israel |

| Laurent Fournier | IBM Haifa Research Lab, Israel |

| Moshe Levinger   | IBM Haifa Research Lab, Israel |

| Shmuel Ur        | IBM Haifa Research Lab, Israel |

| Avi Ziv          | IBM Haifa Research Lab, Israel |

#### **HVC Award Committee**

#### Chair

Roderick Bloem, Graz University of Technology, Austria

#### Committee

Armin Biere Johannes Kepler University, Linz, Austria

Ken McMillan Cadence Berkeley Labs

Amos Nov Cadence, Israel

Mauro Pezzè Università degli Studi di Milano Bicocca,

University of Lugano, Italy

David Rosenblum University College London, UK Gil Shurek IBM Haifa Research Lab, Israel

# **Program Committee**

Sharon Barner IBM Haifa Research Lab, Israel Lyes Benalycherif STMicroelectronics, France Eyal Bin IBM Haifa Research Lab, Israel

Roderick Bloem Graz University of Technology, Austria

Jong-Deok Choi Samsung Electronics, Korea

Alessandro Cimatti IRST, Italy

Kerstin Eder University of Bristol, UK

Bernd Finkbeiner Universität des Saarlandes, Germany

#### VIII Organization

Limor Fix Intel, USA

Laurent Fournier IBM Haifa Research Lab, Israel

Orna Grumberg Technion, Israel

Aarti Gupta NEC Labs America, USA

Klaus Havelund NASA's Jet Propulsion Laboratory,

Columbus Tech.

Alan Hu Univ. of British Columbia, Canada Warren Hunt University of Texas, Austin, USA

Daniel Kroening ETH Zürich, Switzerland Tsvi Kuflik University of Haifa, Israel Orna Kupferman Hebrew University, Israel

Mark Last Ben-Gurion University of the Negev, Israel João Lourenco Universidade Nova de Lisboa, Portugal

Sharad Malik Princeton University, USA

Erich Marschner Cadence, USA Ken McMillan Cadence, USA Amos Nov Cadence, Israel Viresh Paruthi IBM, USA Carl Pixlev Synopsys, USA

Andrew Piziali USA

Wolfgang Roesner IBM Austin, USA

Padmanabhan (Peter)

Santhanam IBM Hawthorne, USA

Fabio Somenzi University of Colorado, USA Scott D. Stoller Stony Brook University, USA

Ofer Strichman Technion, Israel

University of Queensland, Australia Paul Strooper

Serdar Tasiran Koc University, Turkey

Shmuel Ur IBM Haifa Research Lab, Israel

Willem Visser SEVEN Networks, USA

Tao Xie North Carolina State University, USA Karen Yorav IBM Haifa Research Lab, Israel

Avi Ziv IBM Haifa Research Lab, Israel

# Additional Reviewers

Jason Baumgartner

Domagoi Babic

Nicolas Blanc

Angelo Brillout

Hana Chockler

Klaus Dräger

Steven German

Naghmeh Ghafari Dan Goldwasser

John Havlicek Robert L. Kanzelman Jean Christophe Madre Yehuda Naveh Sergey Novikov Rotem Oshman Hans-Jörg Peter Zvonimir Rakamaric Smruti R. Sarangi Sven Schewe Avik Sinha Jörn Guy Süß Michael Veksler Georg Weissenbacher Christoph M. Wintersteiger Margaret Wojcicki Cemal Yilmaz

# **Sponsors**

The Organizing Committee of HVC2007 gratefully acknowledges the generous financial support of:

IBM Haifa Research Lab

Cadence Israel

CRI—The Caesarea Edmond Benjamin de Rothschild Foundation Institute for Interdisciplinary Applications of Computer Science.

# **Table of Contents**

# **Invited Talks**

| Simulation vs. Formal: Absorb What Is Useful; Reject What Is Useless                         | 1  |

|----------------------------------------------------------------------------------------------|----|

| Scaling Commercial Verification to Larger Systems                                            | 8  |

| From Hardware Verification to Software Verification: Re-use and Re-learn                     | 14 |

| Where Do Bugs Come from? (Abstract)                                                          | 16 |

| HVC Award                                                                                    |    |

| Symbolic Execution and Model Checking for Testing                                            | 17 |

| Hardware Verification                                                                        |    |

| On the Characterization of Until as a Fixed Point Under Clocked Semantics                    | 19 |

| Reactivity in SystemC Transaction-Level Models                                               | 34 |

| Model Checking                                                                               |    |

| Verifying Parametrised Hardware Designs Via Counter Automata Ales Smrčka and Tomás Vojnar    | 51 |

| How Fast and Fat Is Your Probabilistic Model Checker? An Experimental Performance Comparison | 69 |

# Dynamic Hardware Verification

| Constraint Patterns and Search Procedures for CP-Based Random Test<br>Generation                       | 86  |

|--------------------------------------------------------------------------------------------------------|-----|

| Using Virtual Coverage to Hit Hard-To-Reach Events                                                     | 104 |

| Merging Formal and Testing                                                                             |     |

| Test Case Generation for Ultimately Periodic Paths                                                     | 120 |

| Dynamic Testing Via Automata Learning                                                                  | 136 |

| Formal Verification for Software                                                                       |     |

| On the Architecture of System Verification Environments                                                | 153 |

| Exploiting Shared Structure in Software Verification Conditions $Domagoj~Babi\acute{c}~and~Alan~J.~Hu$ | 169 |

| Delayed Nondeterminism in Model Checking Embedded Systems Assembly Code                                | 185 |

| A Complete Bounded Model Checking Algorithm for Pushdown                                               | 200 |

| Systems                                                                                                | 202 |

| Software Testing                                                                                       |     |

| Locating Regression Bugs                                                                               | 218 |

| The Advantages of Post-Link Code Coverage                                                              | 235 |

| GenUTest: A Unit Test and Mock Aspect Generation Tool                                                  | 252 |

| Author Index                                                                                           | 267 |

# Simulation vs. Formal: Absorb What Is Useful; Reject What Is Useless

#### Alan J. Hu

Department of Computer Science University of British Columbia

**Abstract.** This short paper is the result of the invited talk I gave at the 2007 Haifa Verification Conference. Its purpose is to briefly summarize the main points of my talk and to provide background references. The original talk abstract was, "Dynamic verification (simulation, emulation) and formal verification often live in separate worlds, with minimal interaction between the two camps, yet both have unique strengths that could complement the other. In this talk, I'll briefly enumerate what I believe are the best aspects of each verification style, and then explore some possibilities for drawing on the strengths of both camps."

# 1 The Bruce Lee Approach to Verification

Absorb what is useful. Reject what is useless.

— Bruce Lee

I was invited to give a talk based on my long-standing interest in both dynamic (simulation and emulation) as well as formal verification, and the interplay between them. As I contemplated what to talk about, I recalled Bruce Lee's famous slogan, quoted above. This led to Cindy Eisner suggesting that the talk be entitled "The Bruce Lee Approach to Verification."

Bruce Lee's quote was a reaction against the orthodoxy of traditional martial arts instruction. He was not the first to articulate such a challenge, nor the last, but he is perhaps the most famous.

Fig. 1 lists some general characteristics of traditional martial arts instruction. These characteristics are common to other traditional instructional systems, such as for monks, many traditional arts, or medieval guilds. Such a system is excellent for preserving the traditions of the group, and for deep study of the intricacies of a given tradition. Students develop strong bonds with their fellow students and great reverence for their teacher, their teacher, etc. For example, I trace my T'ai Chi Ch'uan lineage back to Cheng Man-Ch'ing, who founded the sub-style I practice, and from him back to the founder of the Yang style of T'ai Chi Ch'uan, and I hold great reverence and gratitude to my fellow students and my teachers for their abilities and what they have taught me. In some martial arts styles, this reverence is explicitly formalized. For example, in Aikido schools, every class begins and ends by bowing to a portrait of Morihei Ueshiba, the founder of Aikido.

The problem with the traditional style of instruction is that it can lead to group-think. The lack of communication with other styles slows the spread of good ideas and can lead

- Study is in a school led by the master or a group of affiliated masters.

- Introductory classes are in groups, taught by the master or senior students, with the syllabus set by the master(s).

- Advanced study is one-on-one with the master.

- Students interact almost exclusively with fellow students and the master.

- When students travel, they go to tournaments and workshops, where they interact

and compete with others from the same style.

- Students read books, articles, and papers by the masters of their own style.

- Often, students and teachers denigrate other styles.

Fig. 1. Characteristics of Traditional Martial Arts Instruction

to stagnation. Worse, followers of a style can fail to notice their own assumptions and blind-spots. This causes problems when those assumptions don't hold. For example, in my talk, I showed a video clip of a challenge match, in which one fighter was repeatedly defeated by the other, because the losing fighter's training had not prepared him for the types of situations which tended to occur under the rules and conditions of the challenge match. Bruce Lee's quote was a call to break out of the confines of one's style, to explore what other experts and masters have to offer, to challenge one's assumptions and seek out the best ideas from all sources.

How does this relate to verification? Fig. 2 lists some general characteristics of traditional martial arts instruction. Comparing and contrasting Figs. 1 and 2, one can notice some similarities. Although I do not bow to pictures of Ed Clarke and David Dill each morning when I go to work, I do hold great reverence for their expertise and gratitude for what they've taught me.

The problem, of course, is the same sorts of blind spots that result from spending most of one's time in one community. For example, I am from the formal verification community, but I believe I also have a good awareness of, and an open-mind toward, dynamic verification. Last year, I was giving a talk at the 2006 IEEE International Workshop on High-Level Design Validation and Test on some recent work by my student and myself on using formal verification to guide a commercial logic simulator [12]. I thought this work perfectly straddled the division between formal and simulation, but Gil Shurek and Eyal Bin pointed out that I was still stuck in a formal mind-set: I had assumed that "bad states" were specified declaratively, as a logical assertion, but in reality, bad states might only be identifiable by running a large and complex chunk of imperative software code that acts as a checker. I believe I have an approach to handling such checkers (via software model checking), but the fact that I had completely overlooked this issue illustrates a blind-spot I had acquired by my focus on formal verification.

In my talk, I showed examples of how almost any combination of good ideas from the dynamic and formal communities has produced interesting and useful research. This is not an exhaustive list! I am just giving some examples that come to mind, to illustrate the general value of breaking free of one's style and absorbing useful ideas from others.

<sup>&</sup>lt;sup>1</sup> I'm being deliberately obscure, because I don't want to descend into a "My kung fu style is better than yours" debate. :-)

- Study is in a school led by the professor or a group of affiliated professors.

- Introductory classes are in groups, taught by the professor or graduate students, with the syllabus set by the professor(s).

- Advanced study is one-on-one with the professor.

- Students interact almost exclusively with fellow students and the professor.

- When students travel, they go to conferences and workshops, where they interact

and compete with others from the same style.

- Students read books, articles, and papers by the masters of their own style.

- Often, students and teachers denigrate other styles.

Fig. 2. Characteristics of Traditional Computer Science and Electrical Engineering Education

#### 2 Combining Simulation and Formal

#### 2.1 Version 1.0

The most obvious strength of formal verification is its exhaustiveness, and the most obvious strength of simulation is its scalability. Some of the earliest efforts to derive the best of both worlds sought to use a bit of formal verification, to gain coverage, while relying on simulation to handle the size and complexity of real designs. For example, some leading companies combined the two approaches methodologically, using simulation and emulation as the workhorse for verification, but applying formal strategically to small, high-value areas (e.g., complex protocols or algorithms) that were deemed to be particularly bug-prone (e.g., [7]).

Other approaches combined some formal state-space exploration and random simulation into a single tool, using just a little bit of formal analysis to gain some coverage before the formal analysis exploded. Early examples of work along these lines include computing a few pre-images to enlarge target states for random simulation (e.g., [27,29]), under-approximate reachability through partial image computation (e.g., [25]), and more elaborate combinations (e.g., [18]).

These ideas continue to be valuable. However, I believe a finer-grained examination of the strengths of formal and simulation can yield many other valuable ideas.

#### 2.2 Mix and Match: Good Ideas from Formal

At a slightly finer-grained level, what are the key good ideas to extract from the formal verification world?

- 1. Exhaustive analysis is useful! I believe this is a fundamental conceptual breakthrough from the formal verification community in the past 10–15 years. Previously, exhaustive, brute-force algorithms were typically discarded as impractical, but the formal verification community has repeatedly shown the value of exhaustive analysis for solving real problems. Enabling this breakthrough are two key supporting ideas:

- (a) *Smart, Brute Force:* For example, techniques like BDDs, SAT, SMT, and constraint solving are all brute-force techniques at their worst-case core, but considerable effort has made them efficient and practical for many real problems.

- (b) *Abstraction:* This is the other Swiss Army Knife of formal verification. An exhaustive analysis can become tractable if we can group large (possibly infinite) sets of possibilities and analyze them all together.

- 2. *Machine-Readable Specifications*. This is a really good methodological idea that has long been advocated by the formal verification community and has been gaining broader acceptance. Unless "correctness" is specified unambiguously in a machine-readable form, advanced verification tool support is impossible.

Choosing any of the good ideas from the above list and applying them to simulation yields new, good ideas. For example, constrained test generation has been a major practical success, resulting from applying "smart, brute force" techniques like BDDs, SAT, constraint solving, and state-space traversal to the problem of generating input stimuli for simulation (e.g., [19,1,16]). Combining abstraction and simulation yields abstraction-guided simulation, where model-checking an abstracted version of a system yields information that can help a simulator reach a target state (e.g., [28,21,17,14,26,22,12,13]). And bringing formal, declarative, machine-readable specifications to simulation is the foundation behind assertion-based verification (ABV) (e.g., [6]).

#### 2.3 Mix and Match: Good Ideas from Simulation

Similarly, we can try to extract the key good ideas that make simulation so effective. I have identified three:

- Compiled Code. This was a major performance breakthrough for simulation and enables its continued scalability. The point is to execute the model as code, rather than interpreting it as data, resulting in far higher performance. Hardware accelerators for simulation, as well as emulation, are even more extreme versions of this idea.

- 2. *Metrics*. This is a major methodological contribution pioneered by the simulation community. Coverage metrics of some form are needed to measure and report verification progress.

- 3. Domain Expertise. I am not implying that formal verification engineers lack domain expertise. But as I look at the reported research in formal verification versus dynamic verification, the difference is striking: most papers on formal verification describe a general theory for a general class of systems to verify; most papers on dynamic verification are infused with vast amounts of detailed knowledge about the characteristics of the design. This domain expertise has allowed effective verification in practice, despite the theoretically execrable coverage provided by simulation.

As above, we can mix-and-match good ideas from formal and simulation to generate new, good ideas. Some arbitrary examples of domain-specificity being applied to "smart, brute force" include SAT solvers tuned for hardware bounded model checking (e.g., [15]) or automatically retuned for software verification [20]; applied to abstraction yields things like Burch-Dill pipelined processor verification [9]; applied to specification yields everything from broadly applicable, somewhat domain-specific specification

languages like Sugar [5] and ForSpec [3] (the predecessors of PSL and SVA) all the way down to an obscure example from my own work [10], which allows specifying a cycleaccurate MIPS processor simulator in less than 300 lines of code that runs comparably fast to hand-crafted performance simulators.

Mixing-and-matching Simulation Item 2 (Metrics) produces good ideas like a notion of coverage for formal specifications [11], a coverage model based on predicate abstraction [4], and progress metrics for SAT solvers [2,8].

I am particularly fond of the compiled code idea, having started on this idea several years ago, but not having had the opportunity to explore it as much as I'd like. In the late 1990s, I was teaching computer architecture courses, and it was a fairly common observation that every unpredictable branch cost dozens of instructions, and every non-local memory access might cost hundreds or even thousands of instructions. Conversely, operations that could be done in parallel were essentially free. This led me to realize that formal verification algorithms and data structures were making particularly poor use of modern processors, whereas compiled simulation was particularly efficient. My student and I developed a SAT solver for bounded model checking that compiled the circuit into fast, straightline executable code, but also did some learning [8]. On certain examples, it could greatly outperform the leading SAT-solvers of the time. Combining the idea of exploiting compiled code with abstraction also led to interesting work. I have mentioned abstraction-guided simulation above. Some recent work in this area has sought to employ the idea with leading, commercial compiled-code simulators [26,12]. When we did this, we found that the speed advantage of compiled-code simulation was so great that it overwhelmed the effect of the abstraction-guidance, forcing us to develop a much more robust and effective guidance heuristic [13], which has worked well in extensive experiments on large designs. I do not have any good examples of the combination of compiled code and machine-readable, formal specifications, per se, but as mentioned earlier, it is important that formal tools be able to handle the operational, imperative specifications that are common in the simulation world, and for formal specifications to be compilable into an executable form for use with simulators and emulators (e.g., [24,23] are two of my favorite papers along these lines :-)).

#### 3 The Future

We have only scratched the surface of the possible synergies between formal and simulation. For example, I believe there is a deep connection between abstraction and coverage. The fundamental question is why anything works, given that formal verification is not universal in industrial practice, and the theoretical coverage of the set of all possible behaviors provided by simulation is some  $\varepsilon$  fraction of all possibilities. I believe the answer lies in a connection between the informal coverage matrices used to track simulation progress and the existence of a suitable abstraction for model-checking the design.

<sup>&</sup>lt;sup>2</sup> Hana Chockler has looked at the question of abstraction versus her concept of coverage for formal specifications. Here, I am talking instead of the concept of coverage in the simulation sense — the fraction of the behavior space that has been exercised by the simulator.

Summing up, my advice (or Bruce Lee's advice) is:

- Train hard in your own style. Expertise and depth in your area are your foundation.

- Cross-Train: Friendly study and sparring with practitioners of other verification styles helps share good new ideas and illuminate blind spots.

- Learn from other masters, as well as your own.

This advice doesn't just apply to verification!

#### References

- Aharon, A., Goodman, D., Levinger, M., Lichtenstein, Y., Malka, Y., Metzger, C., Molcho, M., Shurek, G.: Test program generation for functional verification of PowerPC processors in IBM. In: 32nd Design Automation Conference, pp. 279–285. ACM/IEEE (1995)

- 2. Aloul, F.A., Sierawski, B.D., Sakallah, K.A.: Satometer: How much have we searched. In: 39th Design Automation Conference, pp. 737–742. ACM/IEEE (2002)

- 3. Armoni, R., Fix, L., Flaisher, A., Gerth, R., Ginsburg, B., Kanza, T., Landver, A., Mador-Haim, S., Singerman, E., Tiemeyer, A., Vardi, M., Zbar, Y.: The ForSpec temporal logic: A new temporal property-specification language. In: Katoen, J.-P., Stevens, P. (eds.) TACAS 2002. LNCS, vol. 2280, pp. 296–311. Springer, Heidelberg (2002)

- Ball, T.: A theory of predicate-complete test coverage and generation. Technical Report MSR-TR-2004-28, Microsoft Research, (April 2004)

- Beer, I., Ben-David, S., Eisner, C., Fisman, D., Gringauze, A., Rodeh, Y.: The temporal logic sugar. In: Berry, G., Comon, H., Finkel, A. (eds.) CAV 2001. LNCS, vol. 2102, pp. 363–367. Springer, Heidelberg (2001)

- Bening, L., Foster, H.: Principles of Verifiable RTL Design: A Functional Coding Style Supporting Verification Processes in Verilog, 2nd edn. Kluwer Academic Publishers, Dordrecht (2001)

- 7. Bentley, B.: High level validation of next generation microprocessors. In: International Workshop on High-Level Design, Validation, and Test, pp. 31–35. IEEE, Los Alamitos (2002)

- 8. Bingham, J.D., Hu, A.J.: Semi-formal bounded model checking. In: Brinksma, E., Larsen, K.G. (eds.) CAV 2002. LNCS, vol. 2404, pp. 280–294. Springer, Heidelberg (2002)

- Burch, J.R., Dill, D.L.: Automatic verification of pipelined microprocessor control. In: Dill, D.L. (ed.) CAV 1994. LNCS, vol. 818, pp. 68–80. Springer, Heidelberg (1994)

- 10. Chang, F.S.-H., Hu, A.J.: Fast specification of cycle-accurate processor models. In: International Conference on Computer Design, pp. 488–492. IEEE, Los Alamitos (2001)

- Chockler, H., Kupferman, O., Vardi, M.Y.: Coverage metrics for temporal logic model checking. In: Margaria, T., Yi, W. (eds.) TACAS 2001. LNCS, vol. 2031, pp. 528–542. Springer, Heidelberg (2001)

- de Paula, F.M., Hu, A.J.: EverLost: A flexible platform for industrial-strength abstractionguided simulation. In: Ball, T., Jones, R.B. (eds.) CAV 2006. LNCS, vol. 4144, pp. 282–285.

Springer, Heidelberg (2006)

- 13. de Paula, F.M., Hu, A.J.: An effective guidance strategy for abstraction-guided simulation. In: 44th Design Automation Conference, pp. 63–68. ACM/IEEE (2007)

- Edelkamp, S., Lluch-Lafuente, A.: Abstraction in directed model checking. In: Workshop on Connecting Planning Theory and Practice, pp. 7–13 (2004)

- 15. Ganai, M.K., Zhang, L., Ashar, P., Gupta, A., Malik, S.: Combining strengths of circuit-based and CNF-based algorithms for a high-performance SAT solver. In: 39th Design Automation Conference, pp. 747–750. ACM/IEEE (2002)

- Geist, D., Farkas, M., Landver, A., Lichtenstein, Y., Ur, S., Wolfsthal, Y.: Coverage-directed test generation using symbolic techniques. In: Srivas, M., Camilleri, A. (eds.) FMCAD 1996. LNCS, vol. 1166, pp. 143–158. Springer, Heidelberg (1996)

- 17. Gupta, A., Casavant, A.E., Ashar, P. Liu, X.G. (Sean), Mukaiyama, A., Wakabayashi, K.: Property-specific testbench generation for guided simulation. In: 7th Asia and South Pacific Design Automation Conference and 15th International Conference on VLSI Design (VLSID), pp. 524–531. IEEE, Los Alamitos (2002)

- 18. Ho, P.-H., Shiple, T., Harer, K., Kukula, J., Damiano, R., Bertacco, V., Taylor, J., Long, J.: Smart simulation using collaborative formal and simulation engines. In: International Conference on Computer-Aided Design, pp. 120–126. IEEE/ACM (2000)

- 19. Ho, R.C., Yang, C.H., Horowitz, M.A., Dill, D.L.: Architecture validation for processors. In: International Symposium on Computer Architecture (1995)

- 20. Hutter, F., Babić, D., Hoos, H.H., Hu, A.J.: Boosting verification by automatic tuning of decision procedures. In: Formal Methods in Computer-Aided Design, pp. 27–34. IEEE Computer Society Press, Los Alamitos (2007)

- 21. Kuehlmann, A., McMillan, K.L., Brayton, R.K.: Probabilistic state space search. In: International Conference on Computer-Aided Design, pp. 574–579. IEEE/ACM (1999)

- 22. Nanshi, K., Somenzi, F.: Guiding simulation with increasingly refined abstract traces. In: 43rd Design Automation Conference, pp. 737–742. ACM/IEEE (2006)

- 23. Ng, K., Hu, A.J., Yang, J.: Generating monitor circuits for simulation-friendly GSTE assertion graphs. In: International Conference on Computer Design, pp. 409–416. IEEE Computer Society Press, Los Alamitos (2004)

- 24. Oliveira, M.T., Hu, A.J.: High-level specification and automatic generation of IP interface monitors. In: 39th Design Automation Conference, pp. 129–134. ACM/IEEE (2002)

- 25. Ravi, K., Somenzi, F.: High-density reachability analysis. In: International Conference on Computer-Aided Design, pp. 154–158. IEEE/ACM (1995)

- Shyam, S., Bertacco, V.: Distance-guided hybrid verification with GUIDO. In: Design Automation and Test in Europe, pp. 1211–1216 (2006)

- 27. Yang, C.H., Dill, D.L.: SpotLight: Best-first search of FSM state space. In: IEEE International High-Level Design Validation and Test Workshops (HLDVT) (1996)

- 28. Yang, C.H., Dill, D.L.: Validation with guided search of the state space. In: 35th Design Automation Conference, pp. 599–604. ACM/IEEE (1998)

- Yuan, J., Shen, J., Abraham, J., Aziz, A.: On combining formal and informal verification. In: Grumberg, O. (ed.) CAV 1997. LNCS, vol. 1254, pp. 376–387. Springer, Heidelberg (1997)

# Scaling Commercial Verification to Larger Systems

#### Robert Kurshan

Cadence Design Systems

**Abstract.** Simulation test coverage does not scale gracefully with growing system design size. Component interactions grow exponentially with the number of system components, while conventional system test at best can increase coverage as a linear function of allotted test time.

Likewise, capacity limitations are commonly cited as the essential gating factor that restricts the application of automatic formal verification (model checking) to at most a few design blocks.

Nonetheless, abstraction has long been used successfully in pilot projects to apply model checking to entire systems. Abstraction in conjunction with guided-random simulation can be used in the same way to increase coverage for conventional test.

While academic use of abstraction is old, its use in the EDA industry's commercial tool sets has been very limited, due to a perception that its use entails an unacceptably disruptive methodology change. It is shown here how quite general data-path abstraction incorporated into a hierarchical design flow can be introduced with only a modest change in methodology. This hierarchical design flow supports verification based on either simulation or model checking that can scale gracefully with increasing design complexity.

#### 1 Introduction

Today, less than 50% of integrated circuit design cost is attributed to synthesis and layout. The major cost of design is debug and verification, amounting to 50% to 80% of the total. Moreover, the relative and absolute costs of debug and verification are growing, as a result of increasing design complexity.

There are two predominant sources of this increasing complexity: the increasing use of embedded software that is so tightly integrated into the hardware that it is hard or impossible to test the hardware and embedded software separately; and an exponential growth in design complexity.

These two sources of complexity offer quite different verification challenges. Verification in the presence of embedded software requires new algorithms, flows and methodologies, as well as abstraction to handle the greater functional complexity introduced by the large additional software design component.

As a design grows in complexity, it gains additional components that function largely in parallel. Since n parallel components of size m leads to  $m^n$  system states, and the complexity of verification grows in proportion to the size of the design state space, it thus grows exponentially with increasing design size.

The challenge of dealing with this complexity growth – both from embedded software and generally increasing design complexity – is what is addressed here.

As a related matter, it is widely held that the cost of fixing a bug grows exponentially with the stage of development at which it is detected and fixed. This is on account of the increasing interactions with other components, as the design is developed. These other components may be required to reflect changes from such fixes. Additionally, over time a developer may forget the details of a design, or may be unavailable to fix a bug, again increasing the cost of debugging as the design matures.

The hierarchical design flow proposed here addresses both the exponentially increasing verification challenge and the ambition to perform debug and verification earlier in the design flow.

Through the use of abstraction, the intractability of design verification is mitigated. Through use of an abstraction-based top-down stepwise refinement hierarchy, design components can be debugged and verified as soon as they are coded, which is at the earliest possible point in the design development flow.

Although a conventional view is that simulation test is not bound by the capacity limitations of model checking, this leaves a wrong impression. The fact that an arbitrarily large design can be fed into the compiler front-end of a simulation tool does not speak to the quality of the simulation that ensues. In fact, both simulation and model checking are equally compromised by design size. In the case of simulation, this is manifest by diminished coverage; in the case of model checking, it is limited capacity. They are two sides of the same coin.

Through hierarchical design, both coverage for simulation and capacity for model checking can be enhanced.

# 2 Abstraction as Divide-and-Conquer

The age-old strategy for dealing with an intractable task is divide-and-conquer. To build the 6M ton virtual monolith that was the Great Pyramid, the task was divided into the assembly of 2.3M blocks, each small enough to handle. Likewise, the key to verifying a large design is to divide it into blocks small enough to verify. To build the virtual pyramid, its component blocks needed to be assembled with great precision. Likewise, to stitch together verified design blocks into a virtual verification of a large design, mathematical precision is required. Otherwise, there is just a jumble of partial verifications that cannot speak to the behavior of the entire design.

Since the verification of large designs is provably intractable, our only hope lies with some form of divide-and-conquer, and that requires mathematical precision. Thus it is fair to say that whatever the future of verification, it necessarily will be based on formal methods. Design components may be verified through model checking or they may be tested with conventional (informal) simulation test. However, the stitching together of these component results into a virtual result for the entire design must be mediated by a formal method.

Compositional verification implements a sort of "horizontal" divide-and-conquer wherein the design is partitioned into its component blocks, abstractions of some blocks are used to verify local properties of other blocks, and then these local properties are used to deduce global properties of the large design. This second part: to deduce global properties of the large design from local properties can be very challenging, and many research papers have resulted from tour-de-force deductions of this type. The difficulties involved preclude this sort of "horizontal" verification from entering the routine commercial design flow.

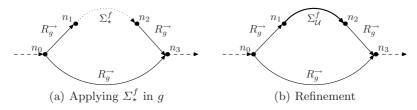

However, there is another sort of divide-and-conquer that can be viewed as "vertical". This is where the design evolves in a top-down fashion that follows a precise stepwise refinement methodology. With "vertical" divide-and-conquer, one begins with certain components together with abstractions of others, as in the "horizontal" case. However, in the "vertical" flow, the abstractions are refined into their ultimate implementations, whereas in the "horizontal" flow, the implementations come first and are then abstracted.

The "vertical" flow cannot in fact be a pure top-down process, as it must end up with a target architecture. In fact, it's a combination top-down/bottomup flow. One starts with the architecture, floor plan, block diagrams, functional specification, etc. as now, and begins coding the design as now, but in a different order.

The "vertical" flow proceeds through stepwise refinement, so that properties may be verified at a high level of abstraction after which they are guaranteed to hold at all subsequent levels of refinement. This facilitates early verification: as soon as a block is coded, it may be verified.

In the "vertical" flow, global properties are verified first, when the design is relatively simple, unencumbered by its low-level implementational details. Properties with greater locality are verified as the relevant blocks are coded, later in the flow. Since they may be verified locally, they do not require large portions of the design to participate in the verification. This flow can maintain a constant-sized granularity for verification, so that coverage and capacity issues are avoided.

# 3 Vertical (Hierarchical) Decomposition

There seems little choice but to code data before control: in order to define a controller, the data objects it controls must have been defined – after all, the controller must refer to the objects it controls. Therefore, today's design flow begins with a coding of the data structures that define data and data paths. Only once these data structures are completely coded may the designer begin to code the finite state machines and other control structures used to control the data.

However, there is something deeply dissatisfying about this order. After all, the controllers define the functional behavior of the design. One would like to define (and debug) them first, and only then code the design infrastructure defined by the data and data paths. It's as if you were required to build a house by first installing the plumbing and wiring, and only after this build the walls and floors.

Coding first the data structures that define data and data paths also leads to design instabilities. Once these data structures are defined, several designers may code controllers against them. However, in coding a controller it is not uncommon for a designer to find the previously coded data structures are insufficient. Perhaps a tag bit required by a controller to store its state in the data path was overlooked. Then the data structures need to be redefined. This may impact several designers and set back the design.

Thus, "data before control" is backward both for the interests of the design process and design stability.

In fact, it is possible to reverse this order for hardware designs and code control before data. This reversal is the key to the "vertical" flow proposed here.

The way to achieve this reversal is to use **stubs** to serve as place-holders for data and data paths. The developer begins the design by coding the controllers, which point to and manipulate these stubs.

These stubs have a semantics, and their refinement into the ultimate data structures that define the data and the data paths is precisely controlled to ensure that the refinement is conservative.

Some stubs are oracles. For example, a controller that needs to move a packet from one buffer to another, conditional on a CRC check of the packet, can be implemented using a stub for the ALU that will perform the CRC check. This stub ALU can be implemented as an oracle that nondeterministically emits a "yes" (CRC passed) or a "no". At a high level of abstraction the packet is also abstracted ("stubbed") as a token, so there is in fact no actual packet to check. At this high level of abstraction, what can be verified is that the controller does the correct action if the answer is "yes" and the correct action if the answer is "no".

Later, the packet stub and the ALU stub will be refined into their actual implementations. At that level it can be checked that the CRC is correct – a local verification independent of the controller. The controller need not be reverified at this lower level, since its correctness is inherited by the conservative refinement process.

Since the controller can be verified as soon as it is coded, it is fresh in the mind of the designer and thus easier to debug. At the same time, the design is simple since much is abstracted (stubbed out), so again debugging is easier. At lower levels of abstraction, debugging is likewise simpler, as at the lower levels the verification is more local, and thus entails smaller portions of the design.

Coding control before data is not an enormous methodology shift: in the end of the design flow, essentially the same RTL code is written as in the present-day flow. The shift is that the design is coded in a different order. All the same considerations of architecture, floor plan and function mediate this new flow just the same as in the old flow. Code must be written in some order; the change proposed here is only that order, not the code itself.

# 4 A Methodology for Hierarchical Design

The crux of the design method proposed here is to code control before data. But which controllers and in what order? The answer lies with a new wrinkle in the design process.

Although most will agree that it is important to define a test plan before design begins, all too often testing is the bastard child of design, left only to the end, to a "verification team" that lies low in the pecking order of the design elite. Leaving testing to the end has been the down-fall of great designs. This is widely understood, and yet astonishingly much less widely accommodated.

The catalyst of the control before data hierarchical design flow is a movement of verification to the top of the development elite. In this flow, the "verification team" gets promoted to become a "specification/verification team". This team works with the same design specifications as the designers, before design coding commences. They derive a complete formal specification of the design using, say, a standardized specification language (PSL, OVL, SVA). These design properties will be used as monitors for simulation test and as assertions and constraints for model checking.

It is important that this design specification be complete, in the sense that collectively the specified properties account for all required design functionality. While there are several criteria for checking "completeness" of a set of design properties that are currently in vogue, such as mutation checks or finite-state machine completeness, each of these have their short-comings.

A better means may be based on the old-fashioned (but time-honored) process of *review*. Just as with a code review where experts analyze a piece of code line-by-line, in a *specification review* the architects, designers and "specification/verification team" review drafts of design properties for correctness and completeness.

Once the specification is complete and deemed correct, the "specification/verification team" establishes a taxonomy of properties, from more global to more local. This taxonomy will drive the order of controller design.

The "specification/verification team" will work hand-in-hand with the designer to establish the order of design coding. Initially, the designer is given a high-level property. The designer codes the controllers required to verify this property, stubbing out the associated data and data paths. The "specification/verification team" will assist the designer in verifying these controllers for the designated property through simulation, model checking or a combination of the two. This way, the controller gets debugged as soon as it is written.

This process continues for other high-level properties, until all the global controllers have been coded and debugged.

Then the stubs are refined (possibly into some data path, some lower-level "local" controllers and new stubs for the remaining data path). The refinements are then verified in their more local context. The locality increases with decreasing granulatity of data. This balance tends to hold the verification complexity constant.

This process continues until all stubs are refined into their ultimate RTL. At this point the design is not only complete, but at the same time, completely verified.

This description serves to give an intuitive understanding of the process that is proposed. In fact, it cannot work as simply as the above description suggests. The refinement flow will not be so neatly linear (top-to-bottom) as this discussion may imply, but will involve imbalanced abstractions at various design levels and non-linear refinement flows. A more detailed description that addresses these realities is beyond the scope of this extended abstract. However, the simplistic linear flow conveys the correct intuition concerning intent and essence of the method.

# From Hardware Verification to Software Verification: Re-use and Re-learn

Aarti Gupta

NEC Laboratories America 4 Independence Way Princeton, NJ 08540, U.S.A.

#### Extended Abstract

With the growing maturity in hardware verification methods, there has been great interest in applying them to verification of software programs. Aside from issues of scale and complexity, there are many differences between the two domains in the underlying problem of searching for bugs. In this talk, I will describe our experiences with this transition, with emphasis on methods that worked and those that did not.

Verification methods based on Boolean Satisfiability (SAT) have emerged as a promising alternative to BDD-based symbolic model checking methods [8]. We have developed an efficient platform for SAT-based model checking [4], called VERISOL, which has been used successfully in industry practice to verify large hardware designs. It uses an efficient circuit representation with on-the-fly simplification algorithms, an incremental hybrid SAT solver, and utilizes several SAT-based engines for finding bugs (bounded model checking) and proofs (proof-based abstraction, SAT-based induction).

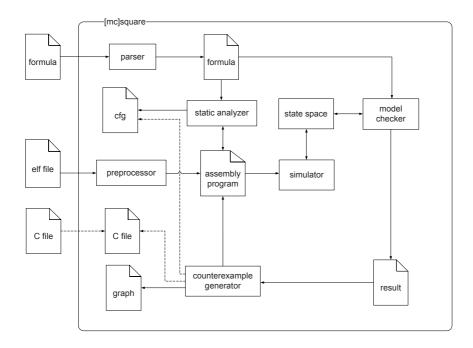

Inspired by its success on hardware designs, we attempted to re-use VERISOL for performing model checking in the back-end of F-SOFT [6], which is targeted for verifying C programs. We first derive a control flow graph (CFG) representation of the program, use static code analyses (program slicing, range analysis, constant folding) to simplify and reduce the CFG, and then derive a symbolic circuit model (under assumptions of finite data and finite recursion). The resulting bit-accurate circuit model of the program is then verified by VERISOL.

Our direct attempt at using hardware verification methods for verifying software models did not lead immediately to success. The two main problems were that the number of variables was too high, and BMC needed to go too deep. We therefore proposed several customized SAT-based heuristics to exploit the high-level structure in CFG models, which greatly improve SAT solver performance [5]. We have also proposed path balancing transformations on the CFG model, which enable additional onthe-fly simplification during BMC to improve performance [3]. To reduce the burden on the model checker, we use program analysis methods for static invariant generation [9] to find proofs more cheaply for array buffer overflow and pointer dereference errors. In our experience, a combination of these methods with SAT-based BMC works much better than predicate abstraction refinement for these checks, since the number of predicates and the number of refinement iterations tend to blow up.

To address the problem of bugs being too deep (when starting from the main function in a C program), we start verification from some intermediate function by

considering a default abstract environment at its interface. This re-uses the idea of a localization reduction [7]. A counterexample reported by the model checker may be spurious due to missing environment information. We use these counterexamples to guide *environment* refinement (*CEGER*). This is similar to standard CEGAR [2] or predicate abstraction refinement [1], except that we use it to refine only the environment, not the model of the program. The CEGER loop is not completely automated – we require help from the user to identify the spurious behavior and guide the refinement. However, the model checker assists the user by providing a concrete error trace, and a weakest precondition as a suggestion for the interface constraint. In practice, users find it much easier to modify a suggested constraint, than to create one.

With these techniques to scale up and supplement model checking for software programs, the F-SOFT platform has recently been used to start an in-house verification service within NEC. To date, it has found more than 450 likely bugs (many confirmed by developers) in four projects totalling 1.1 MLOC (with one 600 kLOC project).

Acknowledgements. I would like to thank the current and past members of the NEC Labs Verification Group – Pranav Ashar, Malay Ganai, Franjo Ivančič, Vineet Kahlon, Weihong Li, Nadia Papakonstantinou, Sriram Sankaranarayanan, Ilya Shlyakhter, Chao Wang, and James Yang – for their numerous contributions to these projects. I would also like to thank Y. Hashimoto, K. Ikeda, S. Iwasaki, A. Mukaiyama, K. Wakabayashi, and the SWED Group from NEC Corp. (Japan) for their support in the development and application of F-SOFT and VERISOL.

#### References

- Ball, T., Majumdar, R., Millstein, T.D., Rajamani, S.K.: Automatic predicate abstraction of C programs. In: ACM SIGPLAN Conference on Programming Language Design and Implementation (2001)

- Clarke, E.M., et al.: Counterexample-guided abstraction refinement. In: Emerson, E.A., Sistla, A.P. (eds.) CAV 2000. LNCS, vol. 1855, pp. 154–169. Springer, Heidelberg (2000)

- 3. Ganai, M.K., Gupta, A.: Accelerating high-level bounded model checking. In: IEEE International Conference on Computer-Aided Design (2006)

- Ganai, M.K., Gupta, A., Ashar, P.: DiVer. In: Halbwachs, N., Zuck, L.D. (eds.) TACAS 2005. LNCS, vol. 3440, pp. 575–580. Springer, Heidelberg (2005)

- Ivančić, F., Shlyakhter, I., Gupta, A., Ganai, M.K., Kahlon, V., Wang, C., Yang, Z.: Model checking C programs using F-SOFT. In: IEEE International Conference on Computer Design (2005)

- Ivančić, F., et al.: F-Soft. In: Etessami, K., Rajamani, S.K. (eds.) CAV 2005. LNCS, vol. 3576, pp. 301–306. Springer, Heidelberg (2005)

- Kurshan, R.P.: Computer-aided Verification of Coordinating Processes: the Automatatheoretic Approach. Princeton University Press, Princeton (1995)

- 8. Prasad, M.R., Biere, A., Gupta, A.: A survey of recent advances in SAT-based formal verification. STTT 7(2), 156–173 (2005)

- Sankaranarayanan, S., et al.: Static analysis in disjunctive numerical domains. In: Yi, K. (ed.) SAS 2006. LNCS, vol. 4134, pp. 3–17. Springer, Heidelberg (2006)

# Where Do Bugs Come from? (Invited Talk)

#### Andreas Zeller

Saarland University, Germany

Abstract. A program fails. How can we locate the cause? A new generation of program analysis techniques automatically determines failure causes even in the absence of any specification - in the input, in the set of code changes, or in the program state: "GCC fails because of a cycle in the abstract syntax tree." Relying on automated tests and dynamic execution data is just one example of how future program analysis techniques will access and leverage data beyond specs and code; leveraging all available data will result in automated assistance for all developer decisions.

# Symbolic Execution and Model Checking for Testing

Corina S. Păsăreanu<sup>1</sup> and Willem Visser<sup>2</sup>

Perot Systems Government Services/NASA Ames Research Center Moffett Field, CA 94035, USA Corina.S.Pasareanu@nasa.gov

<sup>2</sup> SEVEN Networks Redwood City, CA 94063, USA willem@gmail.com

Techniques for checking complex software range from model checking and static analysis to testing. We aim to use the power of exhaustive techniques, such as model checking and symbolic execution, to enable thorough testing of complex software. In particular, we have extended the Java PathFinder model checking tool (JPF) [3] with a symbolic execution capability [4,2] to enable test case generation for Java programs. Our techniques handle complex data structures, arrays, as well as multithreading, and generate optimized test suites that satisfy user-specified testing coverage criteria.

Programs are executed on symbolic, rather than concrete, inputs; the variable values are represented as expressions and constraints that reflect the code structure. JPF generates and analyzes different symbolic execution paths. The input constraints for one path are solved (using off-the-shelf constraint solvers) to generate tests that are guaranteed to execute that path. To bound the search space we put a limit on the model checking search depth, or on the number of constraints along one path. Alternatively, we use abstract state matching [1], which enables JPF to analyze an under-approximation of the program behavior.

Our techniques have been used in black box and white box fashion [5]. They have been applied to generate test sequences for object-oriented code [6] and test vectors for NASA software. Recently, we have also applied our techniques to (executable) models – using a JPF extension for UML Statecharts.

#### References

- Anand, S., Păsăreanu, C.S., Visser, W.: Symbolic execution with abstract subsumption checking. In: Valmari, A. (ed.) SPIN 2006. LNCS, vol. 3925, Springer, Heidelberg (2006)

- Anand, S., Păsăreanu, C.S., Visser, W.: A symbolic execution extension to Java PathFinder. In: Grumberg, O., Huth, M. (eds.) TACAS 2007. LNCS, vol. 4424, Springer, Heidelberg (2007)

K. Yorav (Ed.): HVC 2007, LNCS 4899, pp. 17–18, 2008.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2008

- 3. Java PathFinder. http://javapathfinder.sourceforge.net

- Khurshid, S., Păsăreanu, C.S., Visser, W.: Generalized symbolic execution for model checking and testing. In: Garavel, H., Hatcliff, J. (eds.) ETAPS 2003 and TACAS 2003. LNCS, vol. 2619, Springer, Heidelberg (2003)

- 5. Visser, W., Păsăreanu, C.S., Khurshid, S.: Test input generation with Java PathFinder. In: Proc. ISSTA (2004)

- 6. Visser, W., Păsăreanu, C.S., Pelánek, R.: Test input generation for Java containers using state matching. In: Proc. ISSTA (2006)

# On the Characterization of Until as a Fixed Point Under Clocked Semantics

Dana Fisman<sup>1,2</sup>

$^{1}$  Hebrew University  $^{2}$  IBM Haifa Research Lab

Abstract. Modern hardware designs are typically based on multiple clocks. While a singly-clocked hardware design is easily described in standard temporal logics, describing a multiply-clocked design is cumbersome. Thus, it is desirable to have an easier way to formulate properties related to clocks in a temporal logic. In [6] a relatively simple solution built on top of the traditional LTL semantics was suggested and adopted by the IEEE standard temporal logic PSL. The suggested semantics was examined relative to a list of design goals, and it was shown that it answered all requirements except for preserving the least fixed point characterization of the until operator under multiple clocks. In this work we show that with a minor addition to the semantics of [6] this requirement is met as well.

#### 1 Introduction

Synchronous hardware designs are based on a notion of discrete time, in which the flip-flop (or latch) takes the system from the current state to the next state. A flip-flop or latch is a memory element, which passes on some function of its inputs to its outputs, but only when its clock input is active. The signal that causes the flip-flop (or latch) to transition is termed the *clock*. In a singly-clocked hardware design, temporal operators in logics such as LTL [16,17] are interpreted with respect to the clock, so that the following LTL formula:

$$\mathsf{G}(p \to \mathsf{X}q) \tag{1}$$

can be interpreted as "globally, if p then at the next clock cycle, q". Mapping between a state of a model for the temporal logic and a clock cycle of hardware can then be dealt with by the tool which builds a model from the source code (written in some hardware description language).

Modern hardware designs, however, are typically based on multiple clocks. In such a design, for instance, some flip-flops may be clocked with clka, while others are clocked with clkb. In this case, the mapping between temporal operators and clock cycles cannot be done automatically; rather, the formula itself must contain some indication of which clock to use. Thus, it is desirable to have an easier way to formulate properties related to clocks in a temporal logic. For example, the

linear temporal logic LTL can be extended with a clock operator, denoted  ${\tt @}$ , so that the formula

$$(\mathsf{G}(p \to \mathsf{X}q)) \otimes clka$$

(2)

stating that "globally, if p during a cycle of clka, then at the next cycle of clka, q" will be equivalent to the LTL formula

$$G((clka \land p) \to X(\neg clka \ W \ (clka \land q)))$$

(3)

In [6] a relatively simple solution built on top of the traditional LTL semantics is given. The underlying idea of this solution is that the only role of the clock operator should be to define a projection of the path onto those states where the clock "ticks", and it is its own dual. Actually, referring to a projection of the path is not precisely correct, as we allow access to states in between consecutive states of a projection in the event of a clock switch. However, the word "projection" conveys the intuitive function of the clock operator in the case that the formula is singly-clocked. Achieving this introduces a problem for paths on which the clock never ticks. This problem is solved in [6] by introducing a propositional strength operator that extends the semantics from non-empty paths to empty paths in the same way that the strong next operator [14,12] extends the semantics from infinite paths to finite paths.

The solution of [6] has been adopted by the standard temporal logic PSL [11,5] and extended to account for regular expression which are an important part of PSL. The definition of the clock operator in the standard temporal logic SVA [10] which is based on regular expressions and does not include LTL operators agrees with that of PSL.<sup>1</sup>

The logic given in [6], is measured against a list of design goals. It is shown that all design goals are met, but that the least fixed point characterization of until is not preserved when multiple clocks are involved. The characterization of until as a fixed point is not merely a theoretical issue — it has practical aspects as some tools (e.g. the ones built upon the automata theoretic approach [19]) rely on it. In this work we show that with a minor addition to the semantics of [6] the until operator preserves its least fixed point characterization (and the semantics preserves the other design goals as well).

The addition suggested herein can be thought of as alignment operators, such as those of [9], that takes you to the closest clock tick, when the current cycle is not a clock tick. Note that the next operators takes you to the second clock tick when the current cycle is not a clock tick. This is ok since on the projected path, the second clock tick is the second letter — exactly the place where the next operator will take you in standard LTL. The alignment operator comes in two version, weak and strong, in order to deal with the possibility the clock may stop ticking. The strong alignment operator demands the clock to tick at least once

$<sup>^1</sup>$  PSL stands for *Property Specification Language* and is defined IEEE Std 1850  $^{\rm TM}$  - 2005 [11]. Its formal syntax and semantics are defined in Annex B of this document. SVA stands for *SystemVerilog Assertions* and is defined in Annex E of IEEE Std 1800  $^{\rm TM}$  -2005 [10].

more, while the weak alignment operator makes no such requirement. On singly-clocked formulas there is no need for alignment operators, since a subformula is always evaluated on a clock tick (the clock operator causes the evaluation to consider the projected path, and all other operators keep the evaluation on this path). On multiply-clocked formulas, however, on the event of a clock switch a subformula may be evaluated on a cycle which is not a clock tick. The alignment operators, in this case, takes the evaluation to the closest relevant tick.

The remainder of the paper is organized as follows. In Section 2 we give the semantics of the logic, and explain the difference with [6]. In Section 3 we provide some simple observations on the semantics of the logic. In Section 4 we prove that the least fixed point characterization of until is preserved, as well as the other design goals of [6]. In Section 5 we conclude.

#### 2 The Definition of LTL<sup>®</sup>

The semantics of [6] is defined with respect to a *clock context*. Evaluation of a formula of the form  $\varphi @ clk$  then sets clk to be the clock context. An unclocked formula can be seen as a formula working in clock context true. The temporal operators advance the evaluation according to the clock context. For example, the formula  $\varphi U \psi$  requires that there would be a clock tick of the clock context where  $\psi$  holds and on every preceding tick of the clock  $\varphi$  holds.

The problem of finite paths introduced by the fact that the clock context may stop ticking is solved in [6] by defining two versions of the next operator as is done in LTL [14, pp.272-273] and the linear time  $\mu$ -calculus [12]. The formula X! $\varphi$  of LTL holds on a word w if the length of w is at least two and  $\varphi$  holds on the second letter of w whereas the weak version holds also if the length of w is less than two. In LTL augmented with the clock operator as per [6] we get that X! $\varphi$  holds on a word w if the length of w projected onto the cycles where the clock context ticks is at least two (i.e. there are at least two clock ticks in w) and  $\varphi$  holds on the second tick whereas the weak version holds also if the are less than two ticks. The problem of empty paths introduced by the fact that the clock context may not tick at all is solved in [6] by providing a propositional strength operator. Given a proposition p, both p! and p are formulas of the logic of [6], where the strong version p! holds if on every non-empty word w, the first letter of w satisfies p; and the weak version holds also on the empty word.

In this work we solve the problem of finite and empty paths by augmenting the next operator with an exponent. That is, the next operators comes with a non-negative integer m, so that  $X!^m \varphi$  holds if  $\varphi$  holds on the (m+1)-th future tick of the clock context (where future is understood to include the present). If the clock context is true the formula  $X!^m \varphi$  requires  $\varphi$  to hold on the (m+1)-th letter of the given word. Similarly,  $X^m \varphi$  holds if  $\varphi$  holds on the m+1-th future tick of the clock if there are m+1 future ticks. If the clock context is true the formula  $X^m \varphi$  holds if  $\varphi$  holds on the (m+1)-th letter, or there are less than m+1 letters in the given word. The operators obtained by instantiating m with zero

(i.e. X!<sup>0</sup> and X<sup>0</sup>) can be seen as alignment operators, similar to those of [9].<sup>2</sup> The formulas  $X!^0\varphi$  and  $X^0\varphi$  advance the evaluation to the closest clock tick, when the current cycle is not a clock tick, and evaluate  $\varphi$  there. If the current cycle is a clock tick  $\varphi$  is evaluated at the current cycle. Thus, if the clock context is true(or the formula is unclocked)  $\varphi$  is evaluated at the current letter. As expected the strong version requires that there would be at least one future clock tick while the next version holds also there are no clock ticks. If the clock context is true the strong version requires that the given word would not be empty whereas the weak version holds also if it is empty.

Remark 1. The alignment operators  $X!^0$  and  $X^0$  move to the nearest concurrent or future clock tick. It might be practically useful to include also alignment operators that are strictly future. That is, while X!<sup>0</sup> and X<sup>0</sup> do not advance when the current cycle is a clock tick, the strictly future alignment operators will advance to the next clock tick, when the current cycle is a clock tick (and to the closest clock tick when the current cycle is not a clock tick). These can be defined as syntactic sugaring by means of the existing operators, using T as the clock context.

#### 2.1**Syntax**

We define the syntax of LTL<sup>©</sup> as follows, where we use the term *Boolean expres*sion to refer to any application of the standard Boolean operators to atomic propositions.

# Definition 1 (Formulas of LTL<sup>®</sup>)

- If b is a Boolean expression, then b! and b are LTL $^{\mathfrak{G}}$  formulas.

- If clk is a Boolean expression, m is a non-negative integer, and  $\varphi$  and  $\psi$  are LTL<sup>®</sup> formulas, then the following are LTL<sup>®</sup> formulas:

- $\varphi \wedge \psi$   $X!^m \varphi$   $\varphi U \psi$

Additional operators are derived from the basic operators defined above:

- $\bullet \varphi \lor \psi \stackrel{\text{def}}{=} \neg (\neg \varphi \land \neg \psi)$   $\bullet \mathsf{X}^m \varphi \stackrel{\text{def}}{=} \neg \mathsf{X}!^m \neg \varphi$   $\bullet \mathsf{G} \varphi \stackrel{\text{def}}{=} \neg \mathsf{F} \neg \varphi$   $\bullet \mathsf{X} \varphi \stackrel{\text{def}}{=} \mathsf{X}!^p$   $\bullet \varphi \mathsf{W} \psi \stackrel{\text{def}}{=} (\varphi \mathsf{U} \psi) \lor \mathsf{X} \varphi \stackrel{\text{def}}{=} \mathsf{X}!^p \varphi$

- $\bullet \varphi \mathsf{W} \psi \stackrel{\mathrm{def}}{=} (\varphi \mathsf{U} \psi) \vee \mathsf{G} \varphi$

where T is a Boolean expression that holds on every letter. In the sequel, we also use F, which is a Boolean expression that does not hold for any letter.

We refer to the subset of LTL<sup>®</sup> consisting of the formulas that have no clock operator, by LTL. This subset is a slight generalization of the standard definition

The operators  $X!^0$  and  $X^0$  resemble the operator s\_align Q(c) and w\_align Q(c) of the assertion language ECBV [9]. The definition of the alignment operators here and there do not resemble since the language ECBV is defined by means of computations of an alternating automaton. The obtained semantics, however, does.

of LTL (as defined in [17]) – it consists of two version of Boolean expressions as well as the generalized version of the next operator. The important thing, however, is that it agrees with the standard semantics on the common operators (on non-empty paths, as the standard semantics is defined only over non-empty paths).

#### 2.2 Semantics

We denote a letter by  $\ell$ , and an empty, finite, or infinite word by u, v, or w. The concatenation of u and v is denoted by uv. If u is infinite, then uv = u. The empty word is denoted by  $\epsilon$ , so that  $w\epsilon = \epsilon w = w$ . We denote the length of word v as |v|. The empty word  $\epsilon$  has length 0, a finite word  $v = (\ell_0 \ell_1 \cdots \ell_n)$  has length n+1, and an infinite word has length  $\infty$ . We use i, j, and k to denote non-negative integers. For i < |v| we use  $v^i$  to denote the  $(i+1)^{st}$  letter of v (since counting of letters starts at zero). We denote by  $v^{i\cdots}$  the suffix of v starting at  $v^i$ .

The semantics of LTL<sup>©</sup> is defined inductively with respect to a word (which may be infinite, finite or empty) over the alphabet  $\Sigma = 2^P$  where P is a given non-empty set of atomic propositions. We identify Boolean expression over P as elements of  $B = 2^{2^P}$  (as they convey subset of possible valuations (assignments) to the set of propositions in P). For a Boolean expression  $b \in B$  and a letter  $\ell \in \Sigma$  we define the Boolean satisfaction relation  $\models$  by  $\ell \models b$  iff  $\ell \in b$ .

We first present the semantics of LTL over infinite, finite, and empty words (unclocked semantics). We then present the semantics of LTL<sup>©</sup> over infinite, finite, and empty words (clocked semantics). In Corollary 1 given in Section 4.2 we show that the unclocked semantics can be obtained from the clocked semantics by setting the clock context to T.

**Unclocked Semantics.** We now present semantics for LTL. The semantics is defined with respect to an infinite, finite, or empty word. The notation  $w \models \varphi$  means that formula  $\varphi$  holds along the word w. The semantics is defined as follows, where b denotes a Boolean expression,  $\varphi$  and  $\psi$  denote formulas, and m, j and k denote natural numbers (i.e., non-negative integers).

```

\begin{array}{l} -w \models b \Longleftrightarrow |w| = 0 \text{ or } w^0 \not\models b \\ -w \models b! \iff |w| > 0 \text{ and } w^0 \not\models b \\ -w \models \neg \varphi \iff w \not\models \varphi \\ -w \models \varphi \land \psi \iff w \models \varphi \text{ and } w \models \psi \\ -w \models \mathsf{X}!^m \varphi \iff |w| > m \text{ and } w^{m \cdot \cdot \cdot} \models \varphi \\ -w \models \varphi \mathsf{U} \psi \iff \exists k < |w| \text{ such that } w^{k \cdot \cdot \cdot} \models \psi \text{, and } \forall j < k, \ w^{j \cdot \cdot \cdot} \models \varphi \end{array}

```

Clocked Semantics. We define the semantics of an LTL<sup>®</sup> formula with respect to an infinite, finite, or empty word w and a context c, where c is a Boolean expression over P. We say that a finite word w is a clock tick of clock c if c holds at the last letter of w and does not hold at any previous letter of w. Formally,

#### Definition 2 (clock ticks)

- We say that finite word w is a clock tick of c iff |w| > 0 and  $w^{|w|-1} \models c$  and for every natural number i < |w| - 1,  $w^i \not\models c$ .

- For m > 0, we say that finite word w is m clock ticks of c iff there exists m words  $w_1, w_2, \ldots, w_m$  such that  $w = w_1 w_2 \ldots w_m$  and for every  $1 \le i \le m$ the word  $w_i$  is a clock tick of c.

The notation  $w \stackrel{c}{\models} \varphi$  means that formula  $\varphi$  holds along the word w in the context of clock c. The semantics is defined as follows, where b, c and  $c_1$  denote Boolean expressions,  $\varphi$  and  $\psi$  denote formulas, and m, j and k denote natural numbers (i.e., non-negative integers).

- $-w \stackrel{c}{\models} b \iff \text{if } \exists k < |w| \text{ such that } w^{0..k} \text{ is a clock tick of } c \text{ then } w^k \Vdash b$

- $-w \stackrel{c}{\models} b! \iff \exists k < |w| \text{ such that } w^{0..k} \text{ is a clock tick of } c \text{ and } w^k \Vdash b$

- $-w \stackrel{c}{\vDash} \neg \varphi \iff w \stackrel{c}{\nvDash} \varphi$

- $-w \stackrel{c}{\models} \varphi \wedge \psi \iff w \stackrel{c}{\models} \varphi \text{ and } w \stackrel{c}{\models} \psi$

- $-w \stackrel{c}{\models} \mathsf{X}!^m \varphi \iff \exists j < |w| \text{ s.t. } w^{0..j} \text{ is } m+1 \text{ clock ticks of } c \text{ and } w^{j...} \stackrel{c}{\models} \varphi$

- $-w \stackrel{c}{\models} \varphi \cup \psi \iff \exists k < |w| \text{ such that } w^k \Vdash c \text{ and } w^{k...} \stackrel{c}{\models} \psi \text{ and }$

$$\forall j < k \text{ such that } w^j \models c, w^{j...} \models^c \varphi$$

$$-w \stackrel{c}{\models} \varphi @c_1 \iff w \stackrel{c_1}{\models} \varphi$$

#### Observations on the Semantics of LTL® 3

The following section provides some simple observation regarding the weak/ strong next operators and their exponents. First we provide the direct semantics of the weak next operator, which was given as a syntactic sugaring of the strong next operator in Section 2.1.

Claim 1 (Weak next operator). Let w be a word over  $\Sigma$ . Let c be a Boolean expression in B, m a non-negative integer and  $\varphi$  an LTL<sup>©</sup> formula. Then

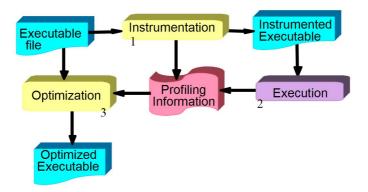

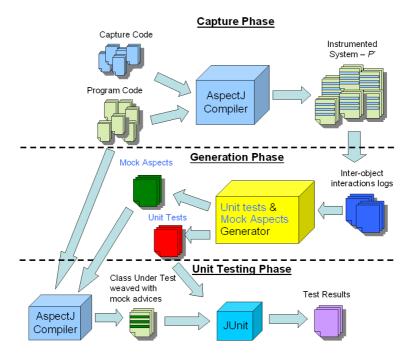

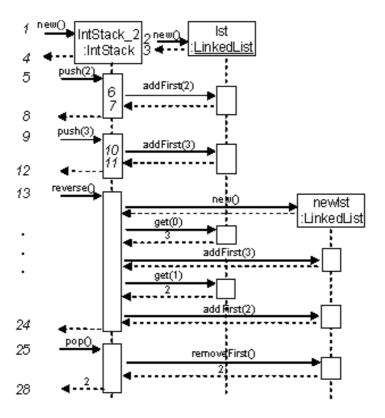

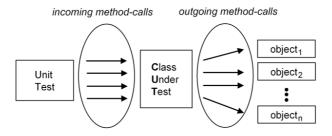

$$w \models^{c} \mathbf{X}^{m} \varphi \Longleftrightarrow \textit{if} \ \exists j < |w| \ \textit{s.t.} \ w^{0..j} \ \textit{is} \ m+1 \ \textit{clock ticks of} \ c \ \textit{then} \ w^{j..} \models^{c} \varphi$$