Speech Processing in Embedded Systems

Priyabrata Sinha

# Speech Processing in Embedded Systems

Priyabrata Sinha Microchip Technology, Inc., Chandler AZ, USA priyabrata.sinha@microchip.com

Certain Materials contained herein are reprinted with permission of Microchip Technology Incorporated. No further reprints or reproductions maybe made of said materials without Microchip's Inc's prior written consent.

ISBN 978-0-387-75580-9 e-ISBN 978-0-387-75581-6 DOI 10.1007/978-0-387-75581-6 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2009933603

#### © Springer Science+Business Media, LLC 2010

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

Speech Processing has rapidly emerged as one of the most widespread and wellunderstood application areas in the broader discipline of Digital Signal Processing. Besides the telecommunications applications that have hitherto been the largest users of speech processing algorithms, several nontraditional embedded processor applications are enhancing their functionality and user interfaces by utilizing various aspects of speech processing. At the same time, embedded systems, especially those based on high-performance microcontrollers and digital signal processors, are rapidly becoming ubiquitous in everyday life. Communications equipment, consumer appliances, medical, military, security, and industrial control are some of the many segments that can potentially exploit speech processing algorithms to add more value to their users. With new embedded processor families providing powerful and flexible CPU and peripheral capabilities, the range of embedded applications that employ speech processing techniques is becoming wider than ever before.

While working as an Applications Engineer at Microchip Technology and helping customers incorporate speech processing functionality into mainstream embedded applications, I realized that there was an acute need for literature that addresses the embedded application and computational aspects of speech processing. This need is not effectively met by the existing speech processing texts, most of which are overwhelmingly mathematics intensive and only focus on theoretical concepts and derivations. Most speech processing books only discuss the building blocks of speech processing but do not provide much insight into what applications and endsystems can utilize these building blocks. I sincerely hope my book is a step in the right direction of providing the bridge between speech processing theory and its implementation in real-life applications.

Moreover, the bulk of existing speech processing books is primarily targeted toward audiences who have significant prior exposure to signal processing fundamentals. Increasingly, the system software and hardware developers who are involved in integrating speech processing algorithms in embedded end-applications are not DSP experts but general-purpose embedded system developers (often coming from the microcontroller world) who do not have a substantive theoretical background in DSP or much experience in developing complex speech processing algorithms. This large and growing base of engineers requires books and other sources of information that bring speech processing algorithms and concepts into the practical domain and also help them understand the CPU and peripheral needs for accomplishing such tasks. It is primarily this audience that this book is designed for, though I believe theoretical DSP engineers and researchers would also benefit by referring to this book as it would provide an real-world implementation-oriented perspective that would help fine-tune the design of future algorithms for practical implementability.

This book starts with Chap. 1 providing a general overview of the historical and emerging trends in embedded systems, the general signal chain used in speech processing applications, several applications of speech processing in our daily life, and a listing of some key speech processing tasks. Chapter 2 provides a detailed analysis of several key signal processing concepts, and Chap. 3 builds on this foundation by explaining many additional concepts and techniques that need to be understood by anyone implementing speech processing applications. Chapter 4 describes the various types of processor architectures that can be utilized by embedded speech processing applications, with special focus on those characteristic features that enable efficient and effective execution of signal processing algorithms. Chapter 5 provides readers with a description of some of the most important peripheral features that form an important criterion for the selection of a suitable processing platform for any application. Chapters 6-8 describe the operation and usage of a wide variety of Speech Compression algorithms, perhaps the most widely used class of speech processing operations in embedded systems. Chapter 9 describes techniques for Noise and Echo Cancellation, another important class of algorithms for several practical embedded applications. Chapter 10 provides an overview of Speech Recognition algorithms, while Chap. 11 explains Speech Synthesis. Finally, Chap. 12 concludes the book and tries to provide some pointers to future trends in embedded speech processing applications and related algorithms.

While writing this book I have been helped by several individuals in small but vital ways. First, this book would not have been possible without the constant encouragement and motivation provided by my wife Hoimonti and other members of our family. I would also like to thank my colleagues at Microchip Technology, including Sunil Fernandes, Jayanth Madapura, Veena Kudva, and others, for helping with some of the block diagrams and illustrations used in this book, and especially Sunil for lending me some of his books for reference. I sincerely hope that the effort that has gone into developing this book helps embedded hardware and software developers to provide the most optimal, high-quality, and cost-effective solutions for their end customers and to society at large.

Chandler, AZ

Priyabrata Sinha

# Contents

| 1 | Introduction                                         | 1  |

|---|------------------------------------------------------|----|

|   | Digital vs. Analog Systems                           | 1  |

|   | Embedded Systems Overview                            | 3  |

|   | Speech Processing in Everyday Life                   | 4  |

|   | Common Speech Processing Tasks                       | 5  |

|   | Summary                                              |    |

|   | References                                           | 7  |

| 2 | Signal Processing Fundamentals                       | 9  |

|   | Signals and Systems                                  | 9  |

|   | Sampling and Quantization                            | 11 |

|   | Sampling of an Analog Signal                         | 12 |

|   | Quantization of a Sampled Signal                     |    |

|   | Convolution and Correlation                          |    |

|   | The Convolution Operation                            | 16 |

|   | Cross-correlation                                    | 17 |

|   | Autocorrelation                                      | 17 |

|   | Frequency Transformations and FFT                    | 20 |

|   | Discrete Fourier Transform                           | 20 |

|   | Fast Fourier Transform                               | 22 |

|   | Benefits of Windowing                                | 24 |

|   | Introduction to Filters                              | 25 |

|   | Low-Pass, High-Pass, Band-Pass and Band-Stop Filters | 25 |

|   | Analog and Digital Filters                           | 28 |

|   | FIR and IIR Filters                                  | 30 |

|   | FIR Filters                                          | 31 |

|   | IIR Filters                                          | 32 |

|   | Interpolation and Decimation                         | 35 |

|   | Summary                                              |    |

|   | References                                           | 36 |

| 3 | Basic Speech Processing Concepts                              | 37 |

|---|---------------------------------------------------------------|----|

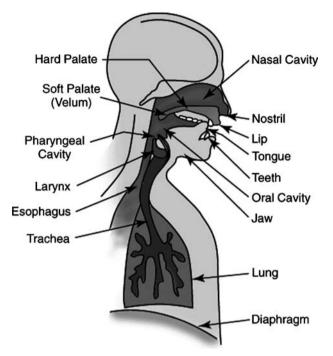

|   | Mechanism of Human Speech Production                          |    |

|   | Types of Speech Signals                                       |    |

|   | Voiced Sounds                                                 |    |

|   | Unvoiced Sounds                                               | 41 |

|   | Voiced and Unvoiced Fricatives                                |    |

|   | Voiced and Unvoiced Stops                                     |    |

|   | Nasal Sounds                                                  |    |

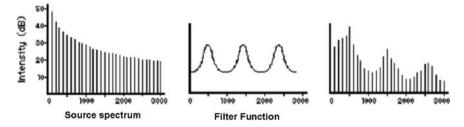

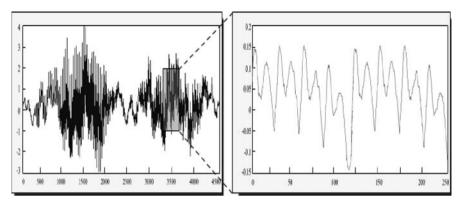

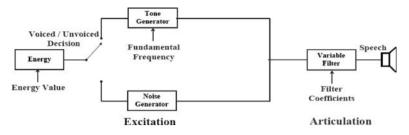

|   | Digital Models for the Speech Production System               |    |

|   | Alternative Filtering Methodologies Used in Speech Processing |    |

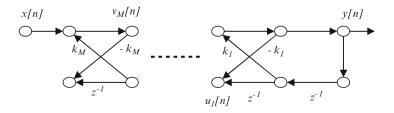

|   | Lattice Realization of a Digital Filter                       |    |

|   | Zero-Input Zero-State Filtering                               |    |

|   | Some Basic Speech Processing Operations                       |    |

|   | Short-Time Energy                                             |    |

|   | Average Magnitude                                             |    |

|   | Short-Time Average Zero-Crossing Rate                         |    |

|   | Pitch Period Estimation Using Autocorrelation                 |    |

|   | Pitch Period Estimation Using Magnitude Difference Function   |    |

|   | Key Characteristics of the Human Auditory System              |    |

|   | Basic Structure of the Human Auditory System                  |    |

|   | Absolute Threshold                                            |    |

|   | Masking                                                       |    |

|   | Phase Perception (or Lack Thereof)                            |    |

|   | Evaluation of Speech Quality                                  |    |

|   | Signal-to-Noise Ratio                                         |    |

|   | Segmental Signal-to-Noise Ratio                               |    |

|   | Mean Opinion Score                                            |    |

|   | Summary                                                       |    |

|   | References                                                    |    |

|   |                                                               | -  |

| 4 | CPU Architectures for Speech Processing                       | 55 |

|   | The Microprocessor Concept                                    | 55 |

|   | Microcontroller Units Architecture Overview                   | 57 |

|   | Digital Signal Processor Architecture Overview                | 59 |

|   | Digital Signal Controller Architecture Overview               | 60 |

|   | Fixed-Point and Floating-Point Processors                     |    |

|   | Accumulators and MAC Operations                               | 62 |

|   | Multiplication, Division, and 32-Bit Operations               |    |

|   | Program Flow Control                                          |    |

|   | Special Addressing Modes                                      |    |

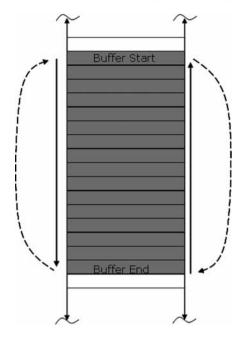

|   | Modulo Addressing                                             |    |

|   | Bit-Reversed Addressing                                       |    |

|   | Data Scaling, Normalization, and Bit Manipulation Support     |    |

|   | Other Architectural Considerations                            |    |

|   | Pipelining                                                    |    |

|   |                                                               |    |

Contents

|   | Memory Caches                                      | 72  |

|---|----------------------------------------------------|-----|

|   | Floating Point Support                             | 73  |

|   | Exception Processing                               |     |

|   | Summary                                            |     |

|   | References                                         |     |

| 5 | Peripherals for Speech Processing                  | 75  |

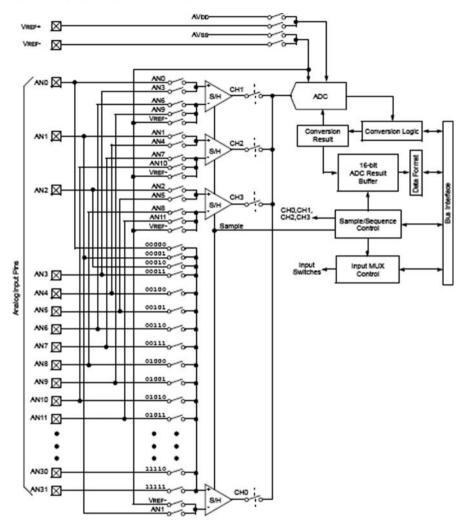

|   | Speech Sampling Using Analog-to-Digital Converters | 75  |

|   | Types of ADC                                       | 76  |

|   | ADC Accuracy Specifications                        | 78  |

|   | Other Desirable ADC Features                       | 79  |

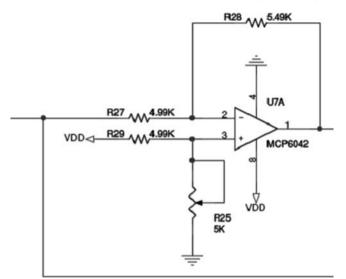

|   | ADC Signal Conditioning Considerations             | 79  |

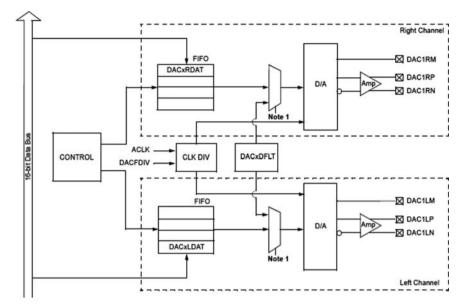

|   | Speech Playback Using Digital-to-Analog Converters | 80  |

|   | Speech Playback Using Pulse Width Modulation       | 81  |

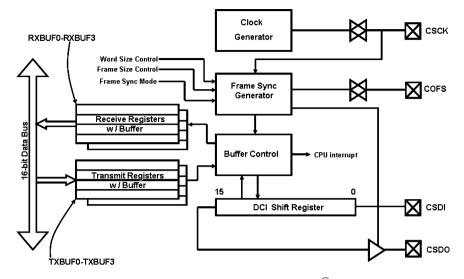

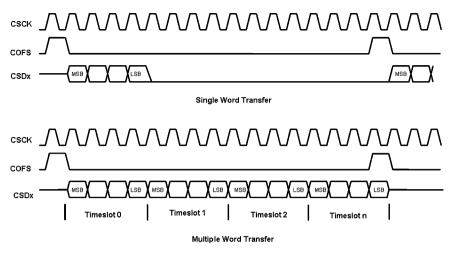

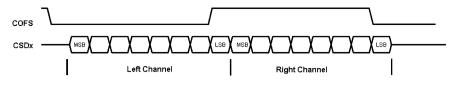

|   | Interfacing with Audio Codec Devices               | 82  |

|   | Communication Peripherals                          | 85  |

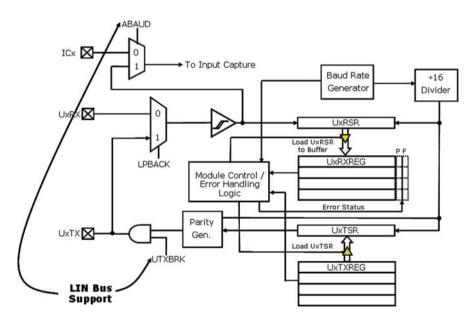

|   | Universal Asynchronous Receiver/Transmitter        | 85  |

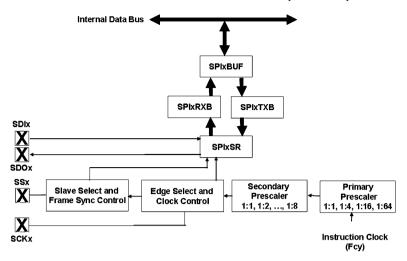

|   | Serial Peripheral Interface                        |     |

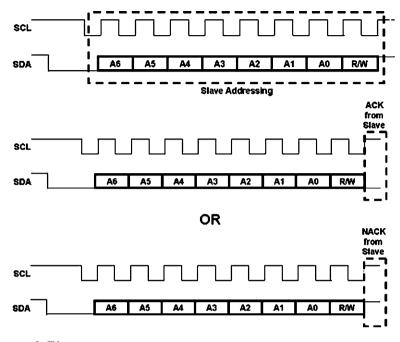

|   | Inter-Integrated Circuit                           |     |

|   | Controller Area Network                            |     |

|   | Other Peripheral Features                          | 90  |

|   | External Memory and Storage Devices                | 90  |

|   | Direct Memory Access                               | 90  |

|   | Summary                                            | 90  |

|   | References                                         | 91  |

| 6 | Speech Compression Overview                        |     |

|   | Speech Compression and Embedded Applications       |     |

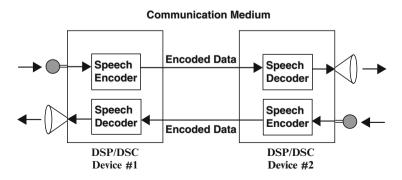

|   | Full-Duplex Systems                                |     |

|   | Half-Duplex Systems                                |     |

|   | Simplex Systems                                    |     |

|   | Types of Speech Compression Techniques             |     |

|   | Choice of Input Sampling Rate                      |     |

|   | Choice of Output Data Rate                         |     |

|   | Lossless and Lossy Compression Techniques          |     |

|   | Direct and Parametric Quantization                 |     |

|   | Waveform and Voice Coders                          |     |

|   | Scalar and Vector Quantization                     |     |

|   | Comparison of Speech Coders                        | 97  |

|   | Summary                                            | 99  |

|   | References                                         | 100 |

|   |                                                    |     |

| 7 | Waveform Coders                                        | 101 |

|---|--------------------------------------------------------|-----|

|   | Introduction to Scalar Quantization                    | 101 |

|   | Uniform Quantization                                   |     |

|   | Logarithmic Quantization                               |     |

|   | ITU-T G.711 Speech Coder                               |     |

|   | ITU-T G.726 and G.726A Speech Coders                   | 105 |

|   | Encoder                                                | 106 |

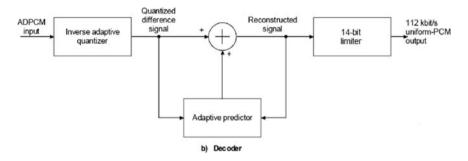

|   | Decoder                                                | 107 |

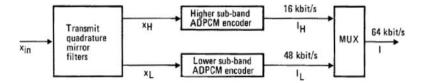

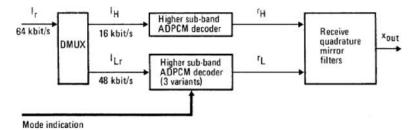

|   | ITU-T G.722 Speech Coder                               | 108 |

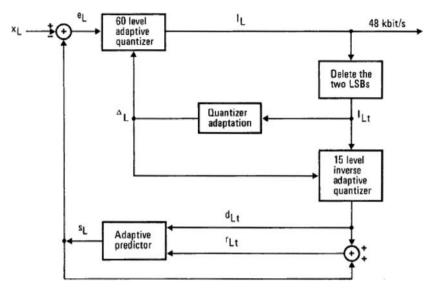

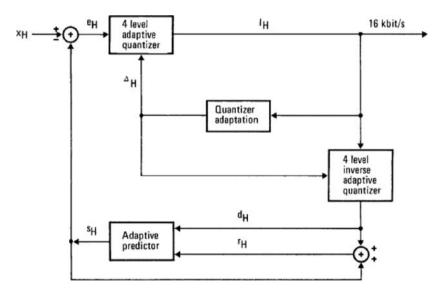

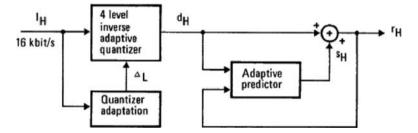

|   | Encoder                                                | 108 |

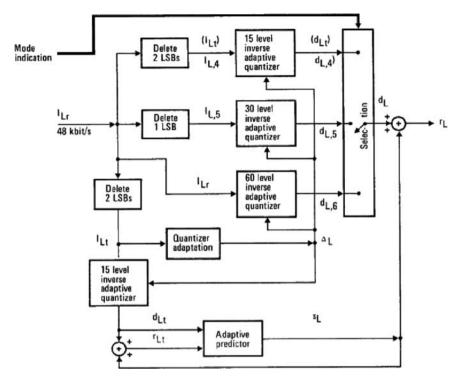

|   | Decoder                                                | 110 |

|   | Summary                                                | 110 |

|   | References                                             | 112 |

| 8 | Voice Coders                                           | 113 |

|   | Linear Predictive Coding                               |     |

|   | Levinson–Durbin Recursive Solution                     |     |

|   | Short-Term and Long-Term Prediction                    |     |

|   | Other Practical Considerations for LPC                 |     |

|   | Vector Quantization                                    |     |

|   | Speex Speech Coder                                     |     |

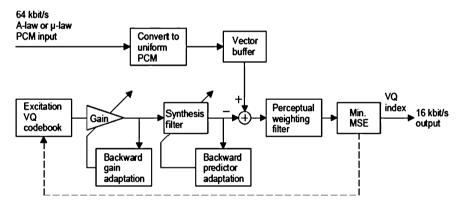

|   | ITU-T G.728 Speech Coder                               |     |

|   | ITU-T G.729 Speech Coder                               |     |

|   | ITU-T G.723.1 Speech Coder                             | 122 |

|   | Summary                                                | 124 |

|   | References                                             | 124 |

| 9 | Noise and Echo Cancellation                            |     |

| - | Benefits and Applications of Noise Suppression         |     |

|   | Noise Cancellation Algorithms for 2-Microphone Systems |     |

|   | Spectral Subtraction Using FFT                         |     |

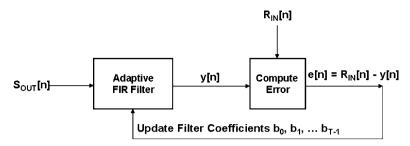

|   | Adaptive Noise Cancellation                            |     |

|   | Noise Suppression Algorithms for 1-Microphone Systems  |     |

|   | Active Noise Cancellation Systems                      |     |

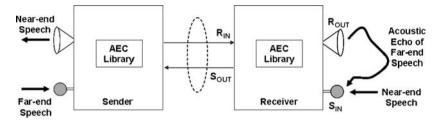

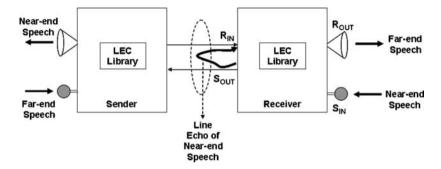

|   | Benefits and Applications of Echo Cancellation         | 136 |

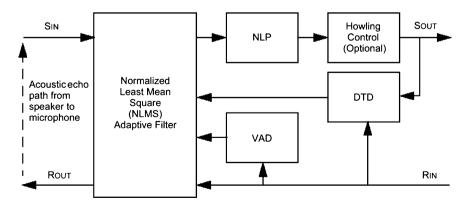

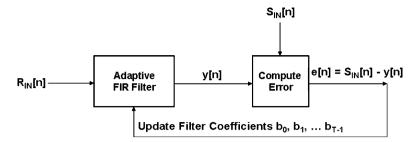

|   | Acoustic Echo Cancellation Algorithms                  |     |

|   | Line Echo Cancellation Algorithms                      |     |

|   | Computational Resource Requirements                    |     |

|   | Noise Suppression                                      |     |

|   | Acoustic Echo Cancellation                             |     |

|   | Line Echo Cancellation                                 |     |

|   | Summary                                                |     |

|   | References                                             |     |

|   |                                                        |     |

Contents

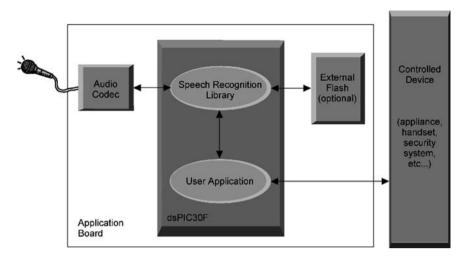

| 10  | Speech Recognition                                          | 143 |

|-----|-------------------------------------------------------------|-----|

|     | Benefits and Applications of Speech Recognition             | 143 |

|     | Speech Recognition Using Template Matching                  | 147 |

|     | Speech Recognition Using Hidden Markov Models               |     |

|     | Viterbi Algorithm                                           |     |

|     | Front-End Analysis                                          |     |

|     | Other Practical Considerations                              |     |

|     | Performance Assessment of Speech Recognizers                |     |

|     | Computational Resource Requirements                         |     |

|     | Summary                                                     |     |

|     | References                                                  |     |

| 11  | Speech Synthesis                                            | 157 |

| ••  | Benefits and Applications of Concatenative Speech Synthesis |     |

|     | Benefits and Applications of Text-to-Speech Systems         |     |

|     | Speech Synthesis by Concatenation of Words and Subwords     |     |

|     | Speech Synthesis by Concatenation of Words and Subwords     |     |

|     | Speech Synthesis by Conversion from Text (TTS)              |     |

|     | Preprocessing                                               |     |

|     | Morphological Analysis                                      |     |

|     | Phonetic Transcription                                      |     |

|     | Syntactic Analysis and Prosodic Phrasing                    |     |

|     | Assignment of Stresses                                      |     |

|     | Timing Pattern                                              |     |

|     | Fundamental Frequency                                       |     |

|     | Computational Resource Requirements                         |     |

|     | Summary                                                     |     |

|     | References                                                  |     |

|     | Keterenees                                                  | 104 |

| 12  | Conclusion                                                  | 165 |

|     | References                                                  | 167 |

| Ind | lex                                                         | 169 |

# Chapter 1 Introduction

The ability to communicate with each other using spoken words is probably one of the most defining characteristics of human beings, one that distinguishes our species from the rest of the living world. Indeed, speech is considered by most people to be the most natural means of transferring thoughts, ideas, directions, and emotions from one person to another. While the written word, in the form of texts and letters, may have been the origin of modern civilization as we know it, talking and listening is a much more interactive medium of communication, as this allows two persons (or a person and a machine, as we will see in this book) to communicate with each other not only instantaneously but also simultaneously.

It is, therefore, not surprising that the recording, playback, and communication of human voice were the main objective of several early electrical systems. Microphones, loudspeakers, and telephones emerged out of this desire to capture and transmit information in the form of speech signals. Such primitive "speech processing" systems gradually evolved into more sophisticated electronic products that made extensive use of transistors, diodes, and other discrete components. The development of integrated circuits (ICs) that combined multiple discrete components together into individual silicon chips led to a tremendous growth of consumer electronic products and voice communications equipment. The size and reliability of these systems were enhanced to the point where homes and offices could widely use such equipment.

# **Digital vs. Analog Systems**

Till recently, most electronic products handled speech signals (and other signals, such as images, video, and physical measurements) in the form of analog signals: continuously varying voltage levels representing the audio waveform. This is true even now in some areas of electronics, which is not surprising since all information in the physical world exists in an essentially analog form, e.g., sound waveforms and temperature variations. A large variety of low-cost electronic devices, signal conditioning circuits, and system design techniques exist for manipulating analog signals; indeed, even modern digital systems are incomplete without some analog components such as amplifiers, potentiometers, and voltage regulators.

However, an all-analog electronic system has its own disadvantages:

- Analog signal processing systems require a lot of electronic circuitry, as all computations and manipulations of the signal have to be performed using a combination of analog ICs and discrete components. This naturally adds to system cost and size, especially in implementing rigorous and sophisticated functionality.

- Analog circuits are inherently prone to inaccuracy caused by component tolerances. Moreover, the characteristics of analog components tend to vary over time, both in the short term ("drift") and in the long term ("ageing").

- Analog signals are difficult to store for later review or processing. It may be possible to hold a voltage level for sometime using capacitors, but only while the circuit is powered. It is also possible to store longer-duration speech information in magnetic media like cassette tapes, but this usually precludes accessing the information in any order other than in time sequence.

- The very nature of an analog implementation, a hardware circuit, makes it very inflexible. Every possible function or operation requires a different circuit. Even a slight upgrade in the features provided by a product, e.g., a new model of a consumer product, necessitates redesigning the hardware, or at least changing a few discrete component values.

Digital signal processing, on the other hand, divides the dynamic range of any physical or calculated quantity into a finite set of discrete steps and represents the value of the signal at any given time as the binary representation of the step nearest to it. Thus, instead of an analog voltage level, the signal is stored or transferred as a binary number having a certain (system-dependent) number of bits. This helps digital implementations to overcome some of the drawbacks of analog systems [1]:

- The signal value can be encoded and multiplexed in creative ways to optimize the amount of circuit components, thereby reducing system cost and space usage.

- Since a digital circuit uses binary states (0 or 1) instead of absolute voltages, it is less affected by noise, as a slight difference in the signal level is usually not large enough for the signal to be interpreted as a 0 instead of a 1 or vice versa.

- Digital representations of signals are easier to store, e.g., in a CD player.

- Most importantly, substantial parts of digital logic can be incorporated into a microprocessor, in which most of the functionality can be controlled and adjusted using powerful and optimized software programs. This also lends itself to simple upgrades and improvements of product features via software upgrades, effectively eliminating the need to modify the hardware design on products already deployed in the field.

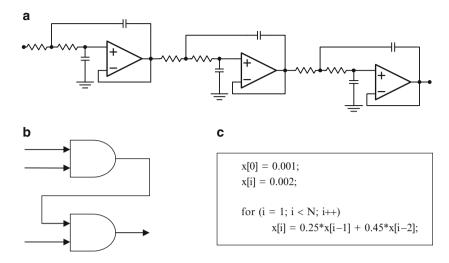

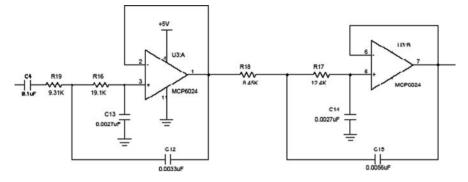

Figure 1.1 illustrates examples of an all-analog system and an all-digital system, respectively. The analog system shown here (an antialiasing filter) can be implemented using op-amps and discrete components such as resistors and capacitors (a). On the contrary, digital systems can be implemented either using digital hardware such as counters and logic gates (b) or using software running on a PC or embedded processor (c).

Fig. 1.1 (a) Example of an analog system, with op-amps and discrete components. (b) Example of a digital system, implemented with hardware logic. (c) Example of a digital system, implemented only using software

#### **Embedded Systems Overview**

We have just seen that the utilization of computer programs running on a microprocessor to describe and control the way in which signals are processed provides a high degree of sophistication and flexibility to a digital system. The most traditional context in which microprocessors and software are used is in personal computers and other stand-alone computing systems. For example, a person's speech can be recorded and saved on the hard drive of a PC and played out through the computer speaker using a media player utility. However, this is a very limited and narrow method of using speech and other physical signals in our everyday life.

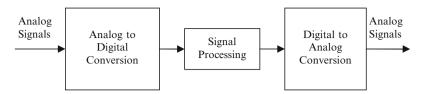

As microprocessors grew in their capabilities and speed of operation, system designers began to use them in settings besides traditional computing environments. However, microprocessors in their traditional form have some limitations when it comes to usage in day-to-day life. Since real-world signals such as speech are analog to begin with, some means must be available to convert these analog signals (typically converted from some other form of energy like sound to electrical energy using transducers) to digital values. On the output path, processed digital values must be converted back into analog form so that they can then be converted to other forms of energy. These transformations require special devices called Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC), respectively. There also needs to be some mechanism to maintain and keep track of timings and synchronize various operations and processes in the system, requiring peripheral devices called Timers. Most importantly, there need to be specialized programmable peripherals to communicate digital data and also to store data values for temporary and

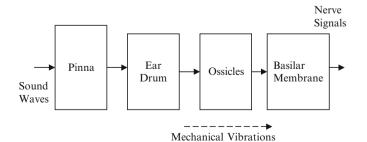

Fig. 1.2 Typical speech processing signal chain

permanent use. Ideally, all these peripheral functions should be incorporated within the processing device itself in order for the control logic to be compact and inexpensive (which is essential especially when used in consumer electronics). Figure 1.2 illustrates the overall speech processing signal chain in a typical digital system.

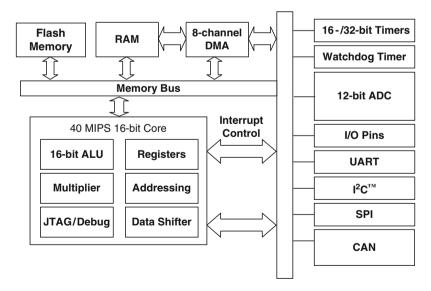

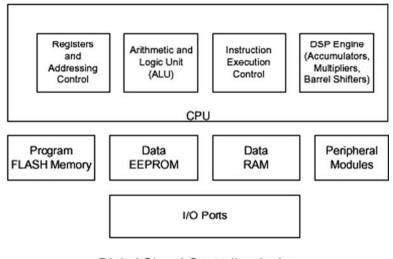

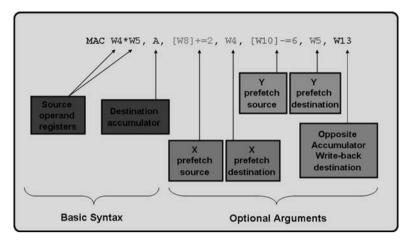

This kind of an integrated processor, with on-chip peripherals, memory, as well as mechanisms to process data transfer requests and event notifications (collectively known as "interrupts"), is referred to as Micro-Controller Units (MCU), reflecting their original intended use in industrial and other control equipment. Another category of integrated microprocessors, specially optimized for computationally intensive tasks such as speech and image processing, is called a Digital Signal Processor (DSP). In recent years, with an explosive increase in the variety of controloriented applications using digital signal processing algorithms, a new breed of hybrid processors have emerged that combines the best features of an MCU and a DSP. This class of processors is referred to as a Digital Signal Controller (DSC) [7]. We shall explore the features of a DSP, MCU, and DSC in greater detail, especially in the context of speech processing applications, in Chaps. 4 and 5.

Finally, it may be noted that some general-purpose Microprocessors have also evolved into Embedded Microprocessors, with changes designed to make them more suitable for nontraditional applications.

Chapters 4 and 5 will describe the CPU and peripheral features in typical DSP/DSC architectures that enable the efficient implementation of Speech Processing operations.

#### Speech Processing in Everyday Life

The proliferation of embedded systems in consumer electronic products, industrial control equipment, automobiles, and telecommunication devices and networks has brought the previously narrow discipline of speech signal processing into everyday life. The availability of low-cost and versatile microprocessor architectures that can be integrated into speech processing systems has made it much easier to incorporate speech-oriented features even in applications not traditionally associated with speech or audio signals.

Perhaps the most conventional application area for speech processing is Telecommunications. Traditional wired telephone units and network equipment are now overwhelmingly digital systems, employing advanced signal processing techniques like speech compression and line echo cancellation. Accessories used with telephones, such as Caller ID systems, answering machines, and headsets are also major users of speech processing algorithms. Speakerphones, intercom systems, and medical emergency notification devices have their own sophisticated speech processing requirements to allow effective and clear two-way communications, and wireless devices like walkie-talkies and amateur radio systems need to address their communication bandwidth and noise issues. Mobile telephony has opened the floodgates to a wide variety of speech processing techniques to allow optimal use of bandwidth and employ value-added features like voice-activated dialing. Mobile hands-free kits are widely used in an automotive environment.

Industrial control and diagnostics is an emerging application segment for speech processing. Devices used to test and log data from industrial machinery, utility meters, network equipment, and building monitoring systems can employ voice-prompts and prerecorded audio messages to instruct the users of such tools as well as user-interface enhancements like voice commands. This is especially useful in environments wherein it is difficult to operate conventional user interfaces like keypads and touch screens. Some closely related applications are building security panels, audio explanations for museum exhibits, emergency evacuation alarms, and educational and linguistic tools. Automotive applications like hands-free kits, GPS devices, Bluetooth headsets/helmets, and traffic announcements are also fast emerging as adopters of speech processing.

With ever-increasing acceptance of speech signal processing algorithms and inexpensive hardware solutions to accomplish them, speech-based features and interfaces are finding their way into the home. Future consumer appliances will incorporate voice commands, speech recording and playback, and voice-based communication of commands between appliances. Usage instructions could be vocalized through synthesized speech generated from user manuals. Convergence of consumer appliances and voice communication systems will gradually lead to even greater integration of speech processing in devices as diverse as refrigerators and microwave ovens to cable set-top boxes and digital voice recorders.

Table 1.1 lists some common speech processing applications in some key market segments: Telecommunications, Automotive, Consumer/Medical, and Industrial/Military. This is by no means an exhaustive list; indeed, we will explore several speech processing applications in the chapters that follow. This list is merely intended to demonstrate the variety of roles speech processing plays in our daily life (either directly or indirectly).

#### **Common Speech Processing Tasks**

Figure 1.3 depicts some common categories of signal processing tasks that are widely required and utilized in Speech Processing applications, or even general-purpose embedded control applications that involve speech signals.

| Telecom                                              | Automotive                               | Consumer/medical                                | Industrial/military                     |  |

|------------------------------------------------------|------------------------------------------|-------------------------------------------------|-----------------------------------------|--|

| Intercom systems Car mobile<br>hands-free kits       |                                          | Talking toys                                    | Test equipment with spoken instructions |  |

| Speakerphones Talking GPS units                      |                                          | Medical emergency phones                        | Satellite phones                        |  |

| Walkie-talkies Voice recorders<br>during car service |                                          | Appliances with spoken instructions             | Radios                                  |  |

| Voice-over-IP Voice activated<br>phones dialing      |                                          | Recorders for<br>physician's notes              | Noise cancelling<br>helmets             |  |

| Analog telephone<br>adapters                         | Voice instructions<br>during car service | Appliances with voice<br>record and<br>playback | Public address systems                  |  |

| Mobile phones Public announcement systems            |                                          | Bluetooth headsets                              | Noise cancelling<br>headsets            |  |

| Telephones Voice activated car<br>controls           |                                          | Dolls with customized voices                    | Security panels                         |  |

| Speech<br>Processing Algorithms                      |                                          |                                                 |                                         |  |

Speech/Speaker Recognition

Speech

Synthesis

Acoustic/Line Echo

Cancellation

Table 1.1 Speech processing application examples in various market segments

Fig. 1.3 Popular signal processing tasks required in speech-based applications

Noise Cancellation

Speech Encoding

and Decoding

Most of these tasks are fairly complex, and are detailed topics by themselves, with a substantial amount of research literature about them. Several embedded systems manufacturers (particularly DSP and DSC vendors) also provide software libraries and/or application notes to enable system hardware/software developers to easily incorporate these algorithms into their end-applications. Hence, it is often not critical for system developers to know the inner workings of these algorithms, and a knowledge of the corresponding Application Programming Interface (API) might suffice.

However, in order to make truly informed decisions about which specific speech processing algorithms are suitable for performing a certain task in the application, it is necessary to understand these techniques to some degree. Moreover, each of these speech processing tasks can be addressed by a tremendous variety of different algorithms, each with different sets of capabilities and configurations and providing different levels of speech quality. The system designer would need to understand

#### References

the differences between the various available algorithms/techniques and select the most effective algorithm based on the application's requirements. Another significant factor that cannot be analyzed without some Speech Processing knowledge is the computational and peripheral requirements of the technique being considered.

## **Summary**

For the above reasons, and also to facilitate a general understanding of Speech Processing concepts and techniques among embedded application developers for whom Speech Processing might (thought not necessarily) be somewhat unfamiliar terrain, several chapters of this book describe the different classes of Speech Processing operations illustrated in Fig. 1.3. Rather than delving too deep into the mathematical derivations and research evolutions of these algorithms, the focus of these chapters will be primarily on understanding the concepts behind these techniques, their usage in end-applications, as well as implementation considerations.

- Chapters 6–8 explain Speech Encoding and Decoding.

- Chapter 9 describes Noise and Echo Cancellation.

- Chapter 10 describes Speech Recognition.

- Chapter 11 describes Speech Synthesis.

## References

- 1. Proakis JG, Manolakis DG Digital signal processing principles, algorithms and applications, Prentice Hall, 1995.

- 2. Rabiner LR, Schafer RW Digital processing of speech signals, Prentice Hall, 1978.

- 3. Chau WC, Speech coding algorithms, Wiley-Interscience, 2003.

- 4. Spanias AS (1994) Speech coding: a tutorial review. Proc IEEE 82(10):1541-1582.

- 5. Hennessy JL, Patterson DA Computer architecture a quantitative approach, Morgan Kaufmann, 2007.

- 6. Holmes J, Holmes W Speech synthesis and recognition, CRC Press, 2001.

- 7. Sinha P (2005) DSC is an SoC innovation. Electron Eng Times, July 2005, pages 51-52.

- Sinha P (2007) Speech compression for embedded systems. In: Embedded systems conference, Boston, October 2007.

# Chapter 2 Signal Processing Fundamentals

**Abstract** The first stepping stone to understanding the concepts and applications of Speech Processing is to be familiar with the fundamental principles of digital signal processing. Since all real-world signals are essentially analog, these must be converted into a digital format suitable for computations on a microprocessor. Sampling the signal and quantizing it into suitable digital values are critical considerations in being able to represent the signal accurately. Processing the signal often involves evaluating the effect of a predesigned system, which is accomplished using mathematical operations such as convolution. It also requires understanding the similarity or other relationship between two signals, through operations like autocorrelation and cross-correlation. Often, the frequency content of the signal is the parameter of primary importance, and in many cases this frequency content is manipulated through signal filtering techniques. This chapter will explore many of these foundational signal processing techniques and considerations, as well as the algorithmic structures that enable such processing.

# Signals and Systems [1]

Before we look at what signal processing involves, we need to really comprehend what we imply by the term "signal." To put it very generally, a signal is any time-varying physical quantity. In most cases, signals are real-world parameters such as temperature, pressure, sound, light, and electricity. In the context of electrical systems, the signal being processed or analyzed is usually not the physical quantity itself, but rather a time-varying electrical parameter such as voltage or current that simply represents that physical quantity. It follows, therefore, that some kind of "transducer" converts the heat, light, sound, or other form of energy into electrical energy. For example, a microphone takes the varying air pressure exerted by sound waves and converts it into a time-varying voltage. Consider another example: a thermocouple generates a voltage that is roughly proportional to the temperature at the junction between two dissimilar metals. Often, the signal varies not only with time but also spatially; for example, the sound captured by a microphone is unlikely to be the same in all directions.

Fig. 2.1 A sinusoidal waveform – a classic example of an analog signal

At this point, I would like to point out the difference between two possible representations of a signal: analog and digital. An analog representation of a signal is where the exact value of the physical quantity (or its electrical equivalent) is utilized for further analysis and processing. For example, a single-tone sinusoidal sound wave would be represented as a sinusoidally varying electrical voltage (Fig. 2.1). The values would be continuous in terms of both its instantaneous level as well as the time instants in which it is measured. Thus, every possible voltage value (within a given range, of course) has its equivalent electrical representation. Moreover, this time-varying voltage can be measured at every possible instant of time. In other words, the signal measurement and representation system has infinite resolution both in terms of signal level and time. The raw voltage output from a microphone or a thermocouple, or indeed from most sensor elements, is essentially an analog signal; it should also be apparent that most real-world physical quantities are really analog signals to begin with!

So, how does this differ from a digital representation of the same signal? In digital format, snapshots of the original signal are measured and stored at regular intervals of time (but not continuously); thus, digital signals are always "discrete-time" signals. Consider an analog signal, like the sinusoidal example we discussed:

$$x_a(t) = A\sin(2\pi F t). \tag{2.1}$$

Now, let us assume that we take a snapshot of this signal at regular intervals of  $T_s = (1/F_s)$  seconds, where  $F_s$  is the rate at which snapshots of the signal are taken. Let us represent  $t/T_s$  as a discrete-time index n. The discrete-time representation of the above signal would be represented as:

$$x_a(nT_s) = A\sin(2\pi F nT_s). \tag{2.2}$$

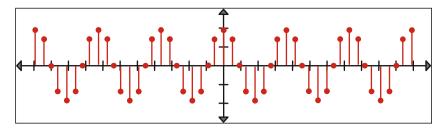

Figure 2.2 illustrates how a "sampled" signal (in this example, a sampled sinusoidal wave) would look like.

Since the sampling interval is known a priori, we can simply represent the above discrete-time signal as an array, in terms of the sampling index *n*. Also,  $F/F_s$  can be denoted as the "normalized" frequency *f*, resulting in the simplified equation:

$$x[n] = A\sin(2\pi f n). \tag{2.3}$$

Fig. 2.2 The sampled equivalent of an analog sinusoidal waveform

However, to perform computations or analysis on a signal using a digital computer (or any other digital circuit for that matter), it is necessary but not sufficient to sample the signal at discrete intervals of time. A digital system of representation, by definition, represents and communicates data as a series of 0s and 1s: it breaks down any numerical quantity into its corresponding binary-number representation. The number of binary bits allocated to each number (i.e., each "analog" value) depends on various factors, including the data sizes supported by a particular digital circuit or microprocessor architecture or simply the way a particular software program may be using the data. Therefore, it is essential for the discrete-time analog samples to be converted to one of a finite set of possible discrete values as well. In other words, not only the sampling intervals but also the sampled signal values themselves must be discrete. From a processing standpoint, it follows that the signal needs to be both "sampled" (to make it discrete-time) and "quantized" (to make it discrete-valued); but more on that later.

The other fundamental concept in any signal processing task is the term "system." A system may be defined as anything (a physical object, electrical circuit, or mathematical operation) that affects the values or properties of the signal. For example, we might want to adjust the frequency components of the signal such that some frequency bands are emphasized more than others, or eliminate some frequencies completely. Alternatively, we might want to analyze the frequency spectrum or spatial signature of the signal. Depending on whether the signal is processed in the analog or digital domain, this system might be an analog signal processing system or a digital one.

## Sampling and Quantization [1,2]

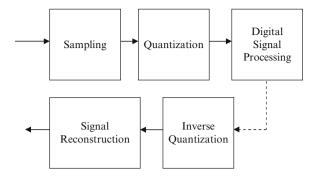

Since real-life signals are almost invariably in an analog form, it should be apparent that a digital signal processing system must include some means of converting the analog signal to a digital representation (through sampling and quantization), and vice versa, as shown in Fig. 2.3.

Fig. 2.3 Typical signal chain, including sampling and quantization of an analog signal

# Sampling of an Analog Signal

As discussed in the preceding section, the level of any analog signal must be captured, or "sampled," at a uniform Sampling Rate in order to convert it to a digital format. This operation is typically performed by an on-chip or off-chip Analog-to-Digital Converter (ADC) or a Speech/Audio Coder–Decoder (Codec) device. While we will investigate the architectural and peripheral aspects of analog-to-digital conversion in greater detail in Chap. 4, it is pertinent at this point to discuss some fundamental considerations in determining the sampling rate used by whichever sampling mechanism has been chosen by the system designer. For simplicity, we will assume that the sampling interval is invariant, i.e., that the sampling is uniform or periodic.

The periodic nature of the sampling process introduces the potential for injecting some spurious frequency components, or "artifacts," into the sampled version of the signal. This in turn makes it impossible to reconstruct the original signal from its samples. To avoid this problem, there are some restrictions imposed on the minimum rate at which the signal must be sampled.

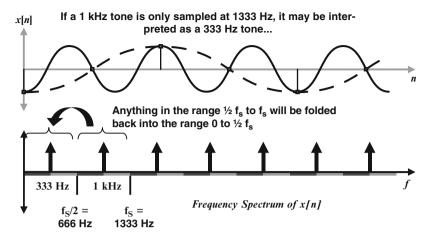

Consider the following simplistic example: a 1-kHz sinusoidal signal sampled at a rate of 1.333 kHz. As can be seen from Fig. 2.4, due to the relatively low sampling rate, several transition points within the waveform are completely missed by the sampling process. If the sampled points are joined together in an effort to interpolate the intermediate missed samples, the resulting waveform looks very different from the original waveform. In fact, the signal now appears to have a single frequency component of 333 Hz! This effect is referred to as Aliasing, as the 1-kHz signal has introduced an unexpected lower-frequency component, or "alias."

The key to avoiding this phenomenon lies in sampling the analog signal at a high enough rate so that at least two (and preferably a lot more) samples within each period of the waveform are captured. Essentially, the chosen sampling rate must satisfy the Nyquist–Shannon Sampling Theorem.

The Nyquist–Shannon Sampling Theorem is a fundamental signal processing concept that imposes a constraint on the minimum rate at which an analog signal must be sampled for conversion into digital form, such that the original signal can

Fig. 2.4 Effect of aliasing caused by sampling less frequently than the Nyquist frequency

Fig. 2.5 A typical analog antialiasing filter, to be used before the signal is sampled

later be reconstructed perfectly. Essentially, it states that this sampling rate must be at least twice the maximum frequency component present in the signal; in other words, the sample rate must be twice the overall bandwidth of the original signal, in our case produced by a sensor.

The Nyquist–Shannon Theorem is a key requirement for effective signal processing in the digital domain. If it is not possible to increase the sampling rate significantly, an analog low-pass filter called Antialiasing Filter should be used to ensure that the signal bandwidth is less than half of the sampling frequency. It is important to note that this filtering must be performed before the signal is sampled, as an aliased signal is already irreversibly corrupted once the sample is sampled.

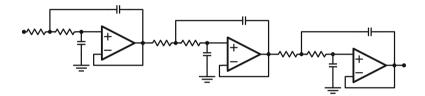

It follows, therefore, that Antialiasing Filters are essentially analog filters that restrict the maximum frequency component of the input signal to be less than half of the sampling rate. A common topology of an analog filter structure used for this purpose is a Sallen–Key Filter, as shown in Fig. 2.5. For speech signals used in telephony applications, for example, it is common to use antialiasing filters that have an upper cutoff frequency at around 3.4 kHz, since the sampling rate is usually 8 kHz.

One possible disadvantage of band-limiting the input signal using antialiasing filters is that there may be legitimate higher-frequency components in the signal that would get rejected as part of the antialiasing process. In such cases, whether to use an antialiasing filter or not is a key design decision for the system designer. In some applications, it may not be possible to sample at a high enough rate to completely avoid aliasing, due to the higher burden this places on the CPU and ADC; in yet other systems, it may be far more desirable to increase the sampling rate significantly (thereby "oversampling" the signal) than to expend hardware resources and physical space on implementing an analog filter. For speech processing applications, the choice of sampling rate is of particular importance, as certain sounds may be more pronounced at the higher range of the overall speech frequency spectrum; but more on that are discussed in Chap. 3.

In any case, several easy-to-use software tools exist to help system designers design antialiasing filters without being concerned with calculating the discrete components and operational amplifiers being used. For instance, the Filter Lab tool from Microchip Technology allows the user to simply enter filter parameters such as cutoff frequencies and attenuation, and the tool generate ready-to-use analog circuit that can be directly implemented in the application.

# Quantization of a Sampled Signal

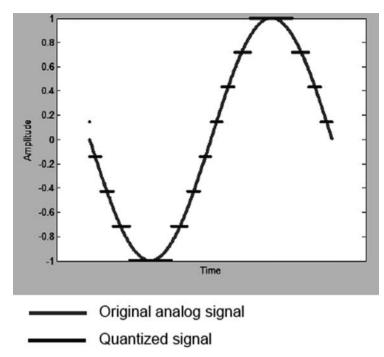

Quantization is the operation of assigning a sampled signal value to one of the many discrete steps within the signal's expected dynamic range. The signal is assumed to only have values corresponding to these steps, and any intermediate values are assigned to the step immediately below it or the step immediately above it. For example, if a signal can have a value between 0 and 5 V, and there are 250 discrete steps, then each step corresponds to a 20-mV range. In this case, 20 mV is denoted as the Quantization Step Size  $\Delta$ . If a signal's sampled level is 1.005 V, then it is assigned a value of 1.00 V, while if it is 1.015 V it is assigned a value of 1.02 V. Thus, quantization is essentially akin to rounding off data, as shown in the simplistic 8-bit quantization example shown in Fig. 2.6.

The number of quantization steps and the size of each step are dependent on the capabilities of the specific analog-to-digital conversion mechanism being used. For example, if an ADC generates 12-bit conversion results, and if it can accept inputs up to 5 V, then the number of quantization steps  $= 2^{12} = 4,096$  and the size of each quantization step is (5/4,096) = 1.22 mV.

In general, if *B* is the data representation in binary bits:

Number of Quantization Steps =

$$2^B$$

, (2.4)

Quantization Step Size =

$$(V_{\text{max}} - V_{\text{min}})/2^B$$

. (2.5)

The effect of quantization on the accuracy of the resultant digital data is generally quantified as the Signal-to-Quantization Noise Ratio (SQNR), which can be computed mathematically as:

$$SQNR = 1.5 \times 2^{(2B)}$$

. (2.6)

Fig. 2.6 Quantization steps for 8-bit quantization

On a logarithmic scale, this can be expressed as:

$$SQNR (dB) = 1.76 + 6.02B.$$

(2.7)

Thus, it can be seen that every additional bit of resolution added to the digital data results in a 6-dB improvement in the SQNR. In general, a high-resolution analog-to-digital conversion alleviates the adverse effect of quantization noise. However, other factors such as the cost of using a higher-resolution ADC (or a DSP with a higher-resolution ADC) as well as the accuracy and linearity specifications of the ADCs being considered. Most standard speech processing algorithms (and indeed, a large proportion of Digital Signal Processing tasks) operate on 16-bit data; so 16-bit quantization is generally considered more than sufficient for most embedded speech applications. In practice, 12-bit quantization would suffice in most applications provided the quantization process is accurate enough.

# **Convolution and Correlation** [2,3]

Convolution and correlation are two extremely popular and fundamental common signal processing operations that are particularly relevant to speech processing, and therefore merit a brief description here. As we will see later, the convolution concept is a building block of digital filtering techniques too. In general, Convolution is a mathematical computation that measures the effect of a system on a signal, whereas Correlation measures the similarity between two signals.

# The Convolution Operation

For now, let us limit our discussion on systems to a linear time-invariant (LTI) system, and let us also assume that both the signal and system are in digital form. A time-invariant system is one whose effect on a signal does not change with time. A linear system is one which satisfies the condition of linearity, which is that if *S* represents the effect of a system on a signal (i.e., system response), and  $x_1[n]$  and  $x_2[n]$  are two input signals, then:

$$S(a_1x_1[n] + a_2x_1[n]) = a_1S(x_1[n]) + a_2S(x_2[n]).$$

(2.8)

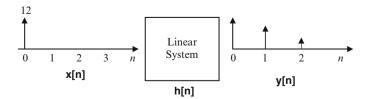

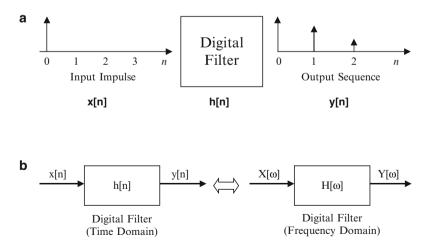

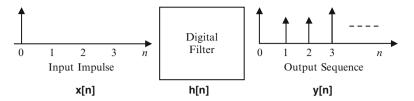

The most common method of describing a linear system is by its Impulse Response. The impulse response of a system is the series of output samples it would generate over time if a unit impulse signal (an instantaneous pulse of infinitesimally small duration which is zero for all subsequent sampling instants) were to be fed as its input. The concept of Impulse Response is illustrated in Fig. 2.7.

Let us denote the discrete-time input signal of interest as x[n], the impulse response of the system as h[n], and the output of the system as y[n]. Then the Convolution is mathematically computed as:

$$y[n] = h[n] \times x[n] = \sum_{k=-\infty}^{+\infty} h[k]x[n-k].$$

(2.9)

Therefore, the convolution sum indicates how the system would behave with a particular signal. A common utility of the Convolution operation is to "smooth" speech signals, i.e., to alleviate the effect that block-processing discontinuities might have on the analysis of a signal.

As we will see in the following sections, this operation is also used to compute the output of a digital filter, one of the most common signal processing tasks in any

Fig. 2.7 Impulse response of a linear digital system

application. There is also a very interesting relationship between the convolution operation and its effect on frequency spectrum, which we will see when we explore the frequency transform of a signal.

#### **Cross-correlation**

The Correlation operation is very similar in its mathematical form to the Convolution. However, in this case the objective is to find the degree of similarity between two input signals relative to the time shift between them. If two different signals are considered the operation is called Cross-correlation, whereas if a signal is correlated with itself it is referred to as Autocorrelation.

Cross-correlation has several uses in various applications; for example, in a sonar or radar application one might find the correlation between the transmitted signal and the received signal for various time delays. In this case, the received signal is simply a delayed version of the transmitted signal, and one can estimate this delay (and thereby the distance of the object that caused the signal to be reflected) by computing the correlation for various time delays.

Mathematically, the cross-correlation between two signals is:

$$r_{xy}[k] = \sum_{n=-\infty}^{+\infty} x[n]y[n-k], \text{ where } k = 0, \pm 1, \pm 2, \text{etc.}$$

(2.10)

It should be apparent from the above equation that for k = 0, the value of the crosscorrelation is maximum when two signals are similar and completely in phase with each other; it would get minimized when two signals are similar but completely out of phase. In general, if two signals are similar in their waveform characteristics, the location of their cross-correlation would indicate how much out of phase they are relative to each other. As a consequence, in some applications where a transmitted signal is reflected back after a certain delay and the application needs to estimate this delay, this can be accomplished by computing the cross-correlation of the transmitted and received (reflected) signals. For instance, this could be used as a simplistic form of echo estimation, albeit for single reflective paths.

#### **Autocorrelation**

For the special case of y[n] = x[n], (2.10) reduces to the following operation, denoted as the Autocorrelation of the signal x[n]:

$$r_{xx}[k] = \sum_{n=-\infty}^{+\infty} x[n]x[n-k], \text{ where } k = 0, \pm 1, \pm 2, \text{ etc.}$$

(2.11)

Fig. 2.8 (a) Random noise signal. (b) Autocorrelation of a random noise signal

Autocorrelation is used to find the similarity of a signal with delayed versions of itself. This is very useful, particularly in evaluating the periodicity of a signal: a perfectly periodic signal will have its highest autocorrelation value when k is the same as its period.

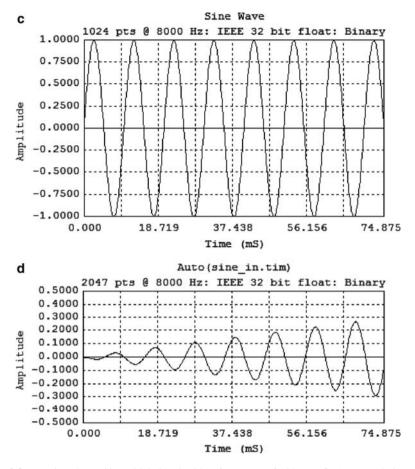

Let us consider an example of a random noise signal, as shown in Fig. 2.8a. Its autocorrelation, shown in Fig. 2.8b, is a sharp peak for a delay of zero and of negligible magnitude elsewhere. On the other hand, the autocorrelation of a periodic sinusoidal signal, shown in Fig. 2.8c, has a prominent periodic nature too, as depicted in Fig. 2.8d.

The above operation is particularly critical in voice coder applications wherein a speech signal might need to be classified into various categories based on its periodicity properties. As we will study in Chap. 3, different types of sounds generated by the human speech generation system have different types of frequency

Fig. 2.8 (continued) (c) Sinusoidal signal with a frequency of 100 Hz. (d) Autocorrelation of a 100-Hz sinusoidal signal

characteristics: some are quasiperiodic whereas others are more like random noise. The Autocorrelation operation, when applied to speech signals, can clearly distinguish between these two types of sounds. Moreover, Autocorrelation can be used to extract desired periodic signals that may be buried in noise, e.g., a sonar wave buried in ambient acoustic noise.

The Autocorrelation operation also has an additional special property that has wide utility in several speech processing and other signal processing applications. When k = 0, the autocorrelation  $r_{xx}[0]$  represents the energy of the signal. If the computation of Autocorrelation is performed over a short range of delays, and repeated for every block of speech signal samples, it can be used to estimate the energy present in that particular segment of speech. This is significant too, as we will learn in Chap. 3.

# Frequency Transformations and FFT [1]

An overwhelming majority of signal processing algorithms and applications require some kind of analysis of the spectral content of a signal. In other words, one needs to find out the strength of each possible frequency component within the signal. There are several popular and not-so-popular methods of computing these frequency components (also known as "frequency bins," if you visualize the overall frequency spectrum of a signal to be comprised of smaller frequency ranges). However, the technique that is by far the most popular, at least as far as Speech Processing is concerned, is the Fourier Transform.

The fundamental principle behind the Fourier Transform is that any signal can be thought of as being composed of a certain number of distinct sinusoidal signals. This implies that one can accurately represent any signal as a linear combination of multiple sinusoidal signals. Therefore, the problem of finding the frequency components of a signal is reduced to finding the frequencies, amplitudes, and phases of the individual sinusoids that make up the overall signal of interest.

The Fourier Transform of a signal x(t) is given by:

$$X(f) = \int_{t=-\infty}^{+\infty} x(t) e^{-j2\pi f t} dt.$$

(2.12)

#### **Discrete Fourier Transform**

When the input signal is sampled at discrete intervals of time, as is the case in Digital Signal Processing algorithms, the above equation can be written in terms of discrete samples x[n] and discrete frequency components X[k]. This formulation is known as the Discrete Fourier Transform (DFT), and is shown below.

$$X[k] = \sum_{n=0}^{N-1} x[n] e^{-j2\pi nk/N},$$

(2.13)

where k = 0, 1, 2, 3, ..., N are the various frequency bins.

Considering a sample rate of Fs, the resolution of the DFT can be given by

Resolution =

$$Fs/N$$

. (2.14)

It is apparent from (2.14) that to achieve a finer analysis of the frequency bins of the signal, the sampling rate should be as less as possible (subject to satisfying the Nyquist–Shannon Theorem, of course) and the processing block size must be as large as possible. Having a large block size comes with a great computational cost in terms of processor speed and memory requirements, and must be carefully evaluated so as to achieve a golden balance between signal processing efficacy and computational efficiency.

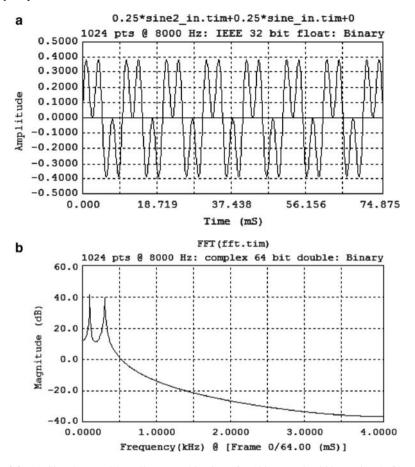

Fig. 2.9 (a) Signal created by a linear combination of a 100-Hz and a 300-Hz signal. (b) DFT frequency spectrum showing distinct 100- and 300-Hz peaks

The DFT completely defines the frequency content of a sampled signal (which is also known as the Frequency Domain representation of the Time Domain signal), as evidenced by the time-domain and frequency-domain plots shown in Fig. 2.9a, b.

Frequency Domain representations are used to "compress" the information of a speech waveform into information about strong frequency components, since not all frequency components are present or even relevant to the application. The frequency spectrum can also be utilized to distinguish between different types of speech sounds, something that has already been mentioned as an important task in some Speech Processing algorithms.

An interesting property of the DFT is that multiplication of two sets of DFT outputs is equivalent to performing the convolution of two blocks of Time Domain data. Thus, if you perform the Inverse DFT of the two sets of Frequency Domain data, and then multiply them point-by-point, the resultant data would be identical to

the convolution of the two signals. This characteristic can be utilized to filter signals in the Frequency Domain rather than the Time Domain.

In general, it is not so much the DFT outputs themselves that are of interest but rather the magnitude and phase of each FFT output. The Squared-Magnitude (which is just as useful as the Magnitude and avoids the computation of a square-root) can be computed as follows:

$$|X[k]|^{2} = \operatorname{Re}[X[k]]^{2} + \operatorname{Im}[X[k]]^{2}$$

(2.15)

and the phase of each FFT output is computed as:

$$\operatorname{Arg}[k] = \arctan\left(\frac{\operatorname{Im}[X[k]]}{\operatorname{Re}[X[k]]}\right).$$

(2.16)

#### Fast Fourier Transform

However, in order to use the DFT operation in a real-time embedded application, it needs to be computationally efficient. An inspection of (2.13) indicates that it requires a large number of mathematical operations, especially when the processing block size is increased. To be precise, it requires N(N - 1) complex multiplications and  $N^2$  complex additions. Remember that a complex addition is actually two real additions, since you need to add the real and imaginary parts of the products. Similarly, each complex multiplication involves four real multiplication operations. Therefore, the order of complexity of the DFT algorithm (assuming all frequency bins are computed) is  $O(N^2)$ . This is obviously not very efficient, especially when it comes to large block sizes (256, 512, 1024, etc.) that are common in many signal processing applications.

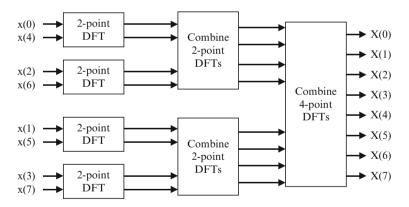

Fortunately, a faster and more popular method exists to compute the DFT of a signal: it is called a Fast Fourier Transform (FFT). There are broadly two classes of FFT algorithms: Decimation in Time (DIT) and Decimation in Frequency (DIF). Both of these are based on a general algorithm optimization methodology called Divideand-Conquer. I shall briefly discuss the core concepts behind the DIT methodology without delving into the mathematical intricacies. The DIF method is left for the reader to study from several good references on this topic, if needed.

The basic principles behind the Radix-2 DIT algorithm (the most popular variant of DIT there is) can be summarized as follows:

- Ensure that the block size N is a power-of-two (which is why it is called a Radix-2 FFT).

- The N-point data sequence is split into two N/2-point data sequences

- Even data samples  $(n = 0, 2, 4, \ldots, N/2)$

- Odd data samples (n = 1, 3, 5, ..., N/2 1).

- Each such sequence is repeatedly split ("decimated") as shown above, finally obtaining N/2 data sequences of only two data samples each. Thus, a larger problem has effectively been broken down into the smallest problem size possible.

- These 2-point FFTs are first computed, an operation popularly known as a "butterfly."

- The outputs of these butterfly computations are progressively combined in successive stages, until the entire N-point FFT has been obtained. This happens when  $\log_2(N)$  stages of computation have been executed.

- The above decimation methodology exploits the inherent periodicity of the  $e^{-j2\pi nk/N}$  term.

A simplified conceptual diagram of an 8-point FFT is shown in Fig. 2.10.

The coefficients  $e^{-j2\pi k/\tilde{N}}$  are the key multiplication factors in the Butterfly computations. These coefficients are called Twiddle Factors, and N/2 Twiddle Factors are required to be stored in memory in order to compute N-point Radix-2 FFT. Since there are only N/2 Twiddle Factors, and since there are  $\log_2(N)$  stages, computing an FFT requires  $(N/2) \log_2(N)$  complex multiplications and  $(N/2) \log_2(N)$ complex additions. This leads to substantial savings in number of mathematical operations, as shown in Table 2.1.

A Radix-4 algorithm can result in a further reduction in number of operations required compared with Radix-2; however, the Radix-4 FFT algorithm requires the

Fig. 2.10 FFT data flow example: 8-point Radix-2 DIT FFT

Table 2.1 Complex multiplications and additions needed by FFT and DFT

|     | DFT             |           | FFT             |           |  |

|-----|-----------------|-----------|-----------------|-----------|--|

| N   | Multiplications | Additions | Multiplications | Additions |  |

| 128 | 16,384          | 16,256    | 448             | 896       |  |

| 256 | 65,536          | 65,280    | 1,024           | 2,048     |  |

| 512 | 262,144         | 261,632   | 2,304           | 4,608     |  |

FFT block size by a power of 4, which is not always feasible to have in many embedded applications. As a result, Radix-2 is by far the most popular form of FFT. The DIF algorithm operates somewhat similar to the DIT algorithm, with one key difference: it is the output data sequence (i.e., the Frequency Domain data) that is decimated in the DIF rather than the input data sequence.

## **Benefits of Windowing**

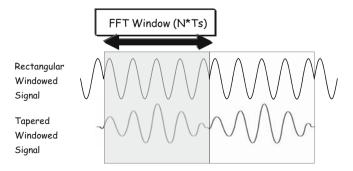

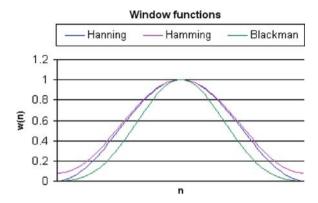

Since a DFT or FFT is computed over a finite number of data points, it is possible that the block sizes and signal frequencies are such that there are discontinuities between the end of one block and the beginning of the next, as illustrated in Fig. 2.11a. These discontinuities manifest themselves as undesirable artifacts in the frequency response, and these artifacts tend to quite spread-out over the spectrum due to their abrupt nature. This can be alleviated somewhat by tapering the edges of the block such that the discontinuities are minimized. This is accomplished very effectively using Window functions.

Window functions are basically mathematical functions of time that impart certain characteristics to the resulting frequency spectrum. They are applied to the input data before computing the FFT, by convolving the impulse response of the Window (Fig. 2.12) with the data samples. This is yet another useful application of the Convolution operation we had seen earlier in this chapter. In practice, application developers may not need to develop software to compute the impulse response of these windows, as processor and third-party DSP. Library vendors often provide ready-to-use functions to compute Window functions. Some of these involve some complicated mathematical operations, but the Window computation need only be performed once by the application and hence does not adversely affect real-time performance in any way.

Now that we have learnt how to analyze the frequency components of any Time Domain signal, let us explore some methods of manipulating the frequencies in the

Fig. 2.11 Discontinuities across FFT blocks, reduced by applying a Window

Fig. 2.12 Impulse response plots of some popular Window functions

signal. Such methods are known as Filters, and are another vital recipe in all signal processing applications; indeed, Digital Filters may be considered the backbone of Digital Signal Processing.

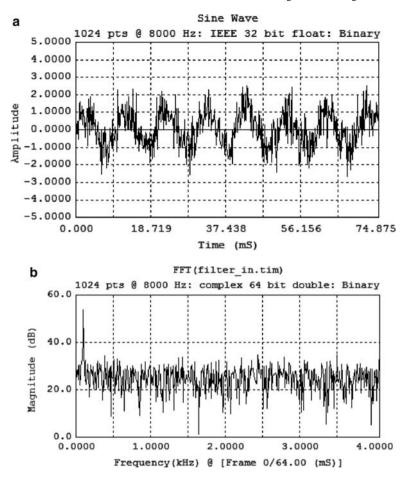

## Introduction to Filters [1]

Filtering is the process of selectively allowing certain frequencies (or range of frequencies) in a signal and attenuating frequency components outside the desired range. In most instances, the objective of filtering is to eliminate or reduce the amount of undesired noise that may be corrupting a signal of interest. In some cases, the objective may simply be to manipulate the relative frequency content of a signal in order to change its spectral characteristics.

For example, consider the time-domain signal illustrated in Fig. 2.13a. Looking at the waveform, it does appear to follow the general envelope of a sinusoidal wave; however, it is heavily corrupted by noise. This is confirmed by looking at the FFT output in Fig. 2.13b, which clearly indicates a sharp peak at 100 Hz but high levels of noise throughout the overall frequency spectrum. In this particular scenario, it is relatively easy to filter the effect of the noise, because the desired signal is concentrated at a specific frequency whereas the noise is equally spread out across all frequencies. This can be done by employing a narrowly selective Band Pass Filter (we will discuss the various types of filters shortly).

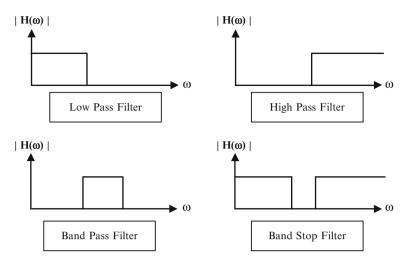

#### Low-Pass, High-Pass, Band-Pass and Band-Stop Filters

Basic filtering problems can be broadly classified into four types:

- Low-Pass Filters

- High-Pass Filters

Fig. 2.13 (a) Sinusoidal signal heavily corrupted by Gaussian noise. (b) Frequency spectrum of the noise-corrupted sinusoidal signal

- Band-Pass Filters

- Band-Stop Filters

The filtering problems stated above differ according to what frequency range is desired relative to the frequency ranges that need to be attenuated, as listed below. Their idealized Frequency Response plots are depicted in Fig. 2.14.

• If it is required to allow frequencies up to a certain cutoff limit and suppress frequency components higher than the cutoff frequency, such a filter is called a Low-Pass Filter. For example, in many systems most of the noise or harmonics may be concentrated at higher frequencies, so it makes sense to perform Low-Pass Filtering.

Fig. 2.14 Different filter types: low pass, high pass, band pass, and band stop

- If it is required to allow frequencies beyond a certain cutoff limit and suppress frequency components lower than the cutoff frequency, such a filter is called a High-Pass Filter. For example, some systems may be affected by DC bias or interference from the mains supply (50 or 60 Hz) which need to be rejected.

- If a certain band of frequencies is required and everything outside this range (either lower or higher) is undesired, then a Band-Pass Filter is the appropriate choice. In many Speech Processing applications, the frequencies of interest may lie in the 200–3,400 Hz range, so anything outside this band can be removed using Band-Pass Filters.

- If a certain band of frequencies needs to be eliminated and everything outside this range (either lower or higher) is acceptable, then a Band-Stop Filter should be used. For example, a signal chain could be affected by certain known sources of noise concentrated at certain frequencies, in which case a Band-Pass Filter (or a combination of multiple filters) could be used to eliminate these noise sources. A highly selective (i.e., narrowband) Band-Pass Filter is also known as a Notch Filter.

At this point, it is pertinent to understand the various parameters, or Filter Specifications, that define the desired response of the filter. It is apparent from Fig. 2.14 that the cutoff frequencies (single frequency in the case of Low-Pass and High-Pass Filters and pair of frequencies in the case of Band-Pass and Band-Stop Filters) are the key parameters. However, these Frequency Responses are idealized and therefore impractical to implement on real hardware or software. Indeed, it is fairly typical to see a band of transition between a point (on the Frequency Spectrum) where the frequency is passed and a nearby point where the frequency is suppressed. Therefore, it is generally necessary to define both the passband frequency and the stopband frequency (or a pair of pass band and stop band frequencies in the case of Band-Pass and Band-Stop Filters); these specifications have a direct bearing on how complex the filter would be to implement (e.g., a sharper transition band implies more computationally intensive filter software).

Another pair of Filter Specifications that directly affect the choice and complexity of filter implementation are the Passband Ripple, Stopband Ripple, and the Stopband Attenuation. All of these parameters are typically expressed in decibels (dB).

- Passband Ripple is the amount of variation of the Frequency Response (and therefore filter output) within the desired Passband.

- Similarly, Stopband Ripple is the amount of variation within the desired Stopband.

- Stopband Attenuation defines the extent by which undesired frequency ranges are suppressed.

# Analog and Digital Filters

Given a certain set of filter specifications, the next choice the application designer would need to make is whether to implement this filter in the Analog or Digital domain. Analog Filtering involves implementing the desired Frequency Response as an analog circuit consisting mostly of operational amplifiers and discrete components such as resistors and capacitors. In some cases, an Analog Filter is absolutely necessary, such as the Antialiasing Filters discussed earlier. In most other instances, however, Digital Filters have distinct advantages over Analog Filters when it comes to implementing in an embedded application, especially one with space, cost, or power consumption constraints. In Chap. 1, we have already seen some general advantages of digital systems over analog systems, so let me simply reiterate some of the key advantages of Digital Filters:

- Digital Filters are less affected by noise. Analog Filters can work quite erratically when subjected to high levels of noise in the system or communication channels.

- Digital Filters are not subject to temperature-related drift in characteristics and also not affected by ageing effects. Both of these are significant constraints on the long-term reliability of Analog Filters.

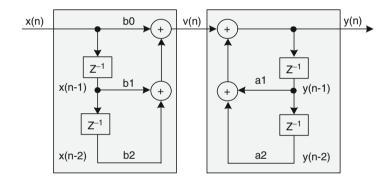

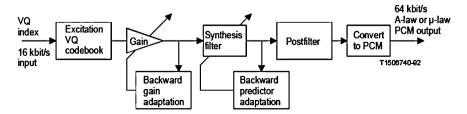

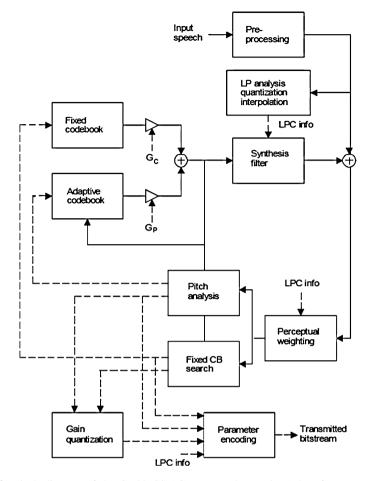

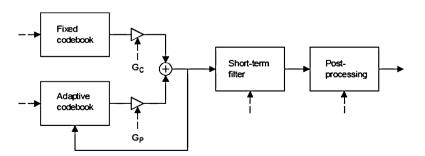

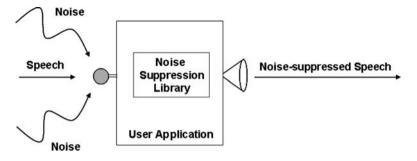

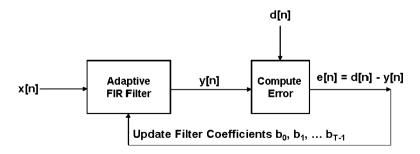

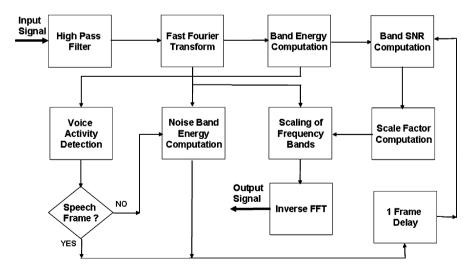

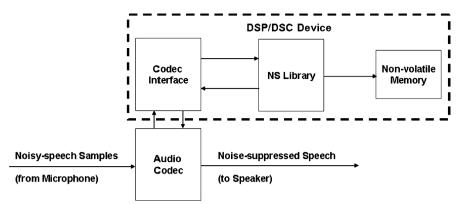

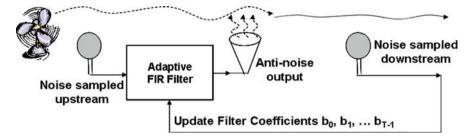

- Digital Filters typically consume less power, which is an enormous advantage in power-sensitive or battery-operated applications such as an Emergency Phone or Walkie-Talkie.